在某远距离测试任务中,需要使用数据采集编码器采集多路高速数字量信号,并将这些信号实时地回传给地面测试台进行数据监测与处理。由于此任务测试环境特殊,测试员不可近距离测试,因此需要将数据在远距离情况下高速地回传给地面测试台进行数据处理。

基于此任务中使用的电缆网所处环境较为恶劣,周围电磁干扰大,本设计在数据回传中选用了CYPRESS公司提出的HOTLink高速串行点对点通信协议,该通信协议采用了PECL电平标准,在协议定义的物理层内容中,用户还可根据需求定义应用层与链路层的协议[1],使用方便灵活且可靠性高;而在逻辑中加入了一种具有纠错能力的BCH编解码方案,可极大地提高数据传输的可靠性。

1 系统总体方案设计

系统的总体设计框图如图1所示,由数据采集编码器、地面测试台及上位机三部分组成。数据采集编码器采集外部高速数字量信号,并将信号数据通过FPGA编帧打包后由HOTLink数据发送模块发送给地面测试台;地面测试台接收到数据后通过PCI9054转发给上位机,数据将在上位机上实时显示;上位机通过地面测试台向数据采集编码器下发一系列指令使其进行相应的动作,指令采用RS-485数据形式收发。

图1 系统总体设计框图

根据测试任务,本设计采用200 m的同轴电缆SFF-50-5连接数据采集编码器与地面测试台,数据采集编码器以330 Mbit/s的码率向地面测试台发送HOTLink数据,并进行大量的实验模拟测试任务的现场条件,通过测试台回读数据的正确性来验证此方案的可行性与可靠性。

2 硬件电路设计

HOTLink发送芯片CY7B923与接收芯片CY7B933是由CYPRESS公司设计,用于高速点对点串行通信[2],其内部自带8B/10B编解码功能,由于8B/10B编码具有直流平衡、转换密度高等优点[3],因此被大量的应用于高速数据传输中,而CY7B923/933也因其具有高可靠性、低功耗、外围电路结构简单等优点[4],被广泛地应用于高速远距离串行通信的场合当中。本设计中CY7B923以及其外围电路位于数据采集编码器中,主要负责将FPGA打包编帧后的数据进行编码并通过同轴电缆发送至地面测试台,而CY7B933以及其外围电路位于地面测试台板卡中,主要负责接收数据采集编码器发来的数据并解码后转发给FPGA进行后续处理。

2.1 CY7B923工作原理及发送电路设计

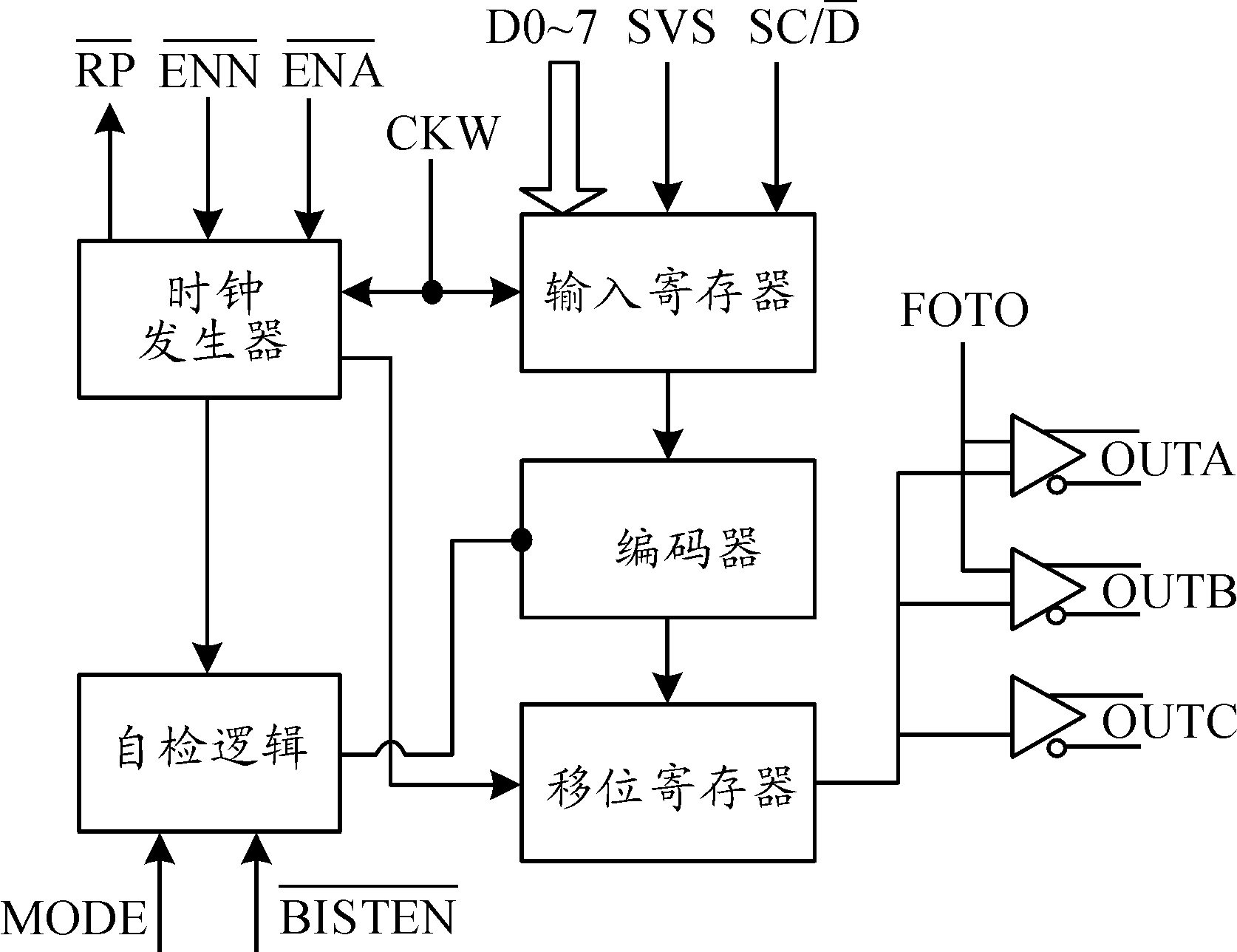

CY7B923内部结构如图2所示,其工作原理为:FPGA控制使能端ENA和ENN的电平以实现时钟上升沿写入数据[5];数据写入后由编码器进行8B/10B编码,并在SC/D电平的控制下将输入数据编码为数据码或控制码;时钟发生器通过内部的PLL锁相环将CKW时钟十倍频后用于驱动移位寄存器;移位寄存器负责将编码器输出的数据转化为串行数据流,并分为3个通道同时输出,FOTO可关闭OUTA±和OUTB±通道输出[6];自检逻辑用于通信系统的自检功能。

图2 CY7B923内部结构框图

图3为CY7B923发送电路图,FPGA输出的8位并行数据通过控制信号由CY7B923编码为串行HOTLink数据;MODE管脚接地表示CY7B923编码方式为8B/10B方式;FIFO接地使数据仅在OUTA±通道输出,将5 V直接接到OUTB±和OUTC±上以降低芯片功耗[7];负载电阻R42和R43连接至GND用于为HOTLink数据输出驱动提供负载电流;C34为去耦电容,用于消除电源耦合;TC1-1T为RF变压器,采用了1∶1的数字隔离变压方式,可以将信号的直流部分滤掉,只保留差分信号用于传输[8],更加有效地抑制共模干扰,增加信号的传输距离;SMDA05LCC为低电容TVS阵列,不仅可以吸收可能造成器件损坏的脉冲,而且能够避免数据受到不必要的噪声影响;SMA-KF3为HOTLink长线传输所用的连接器。

2.2 CY7B933工作原理及接收电路设计

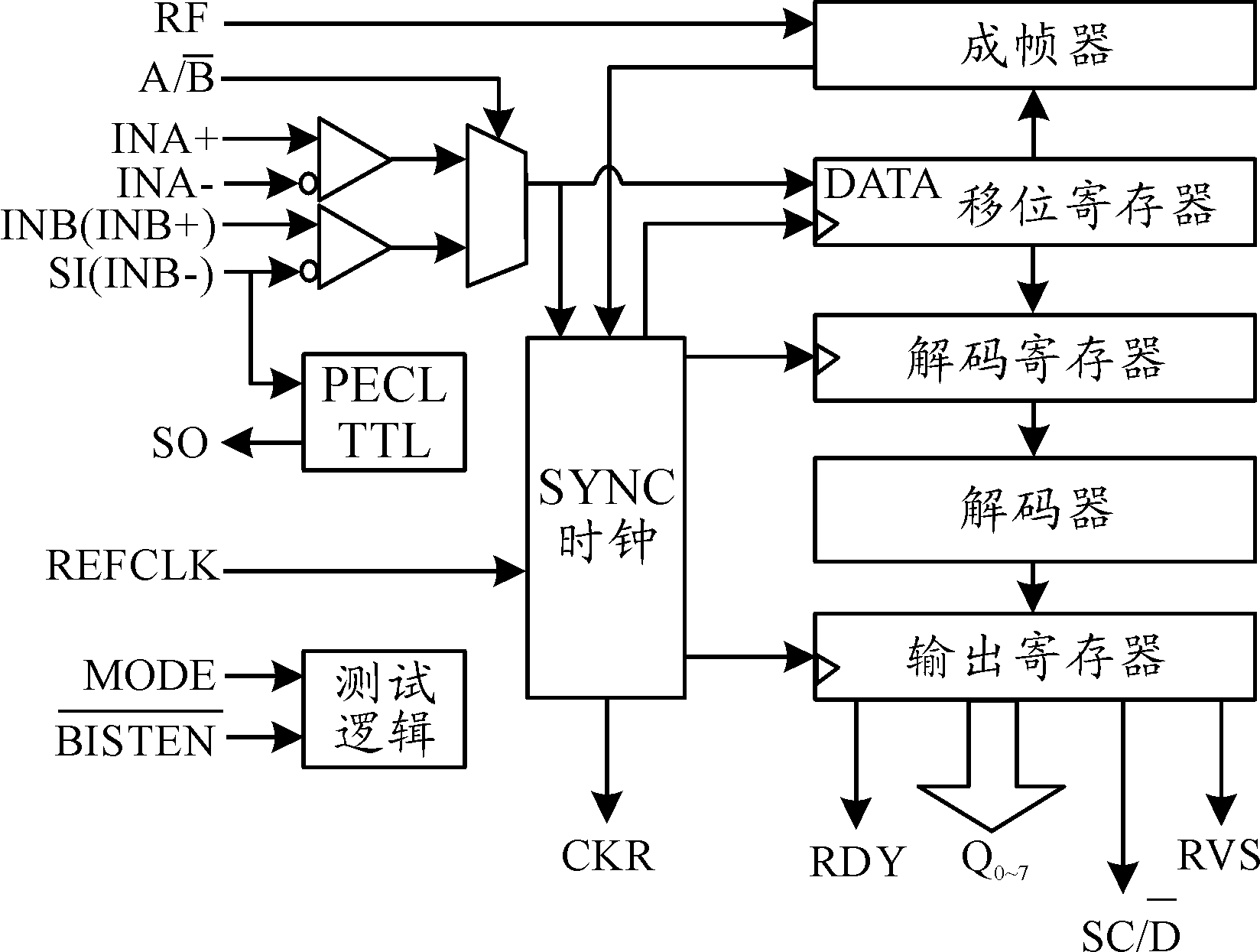

CY7B933内部结构如图4所示,其工作原理为:串行差分输入数据流在A/B端口控制下从INA±或者INB±输入,SYNC时钟模块通过内部PLL锁相环完成时钟的同步功能;在时钟同步下,移位寄存器将输入的串行数据流按字节传送至解码寄存器并按位传送至成帧器[6];成帧器通过查询输入位数据流中定义字节边界的特殊字符从而准确的进行数据组帧;解码寄存器接收到移位寄存器的数据后传送给解码器并一直保持数据直至数据被输出寄存器锁存;解码器根据8B/10B解码表将数据转化为原始数据;输出寄存器保存输出数据并利用CKR同步输出数据。

图3 CY7B923发送电路图

图4 CY7B933内部结构框图

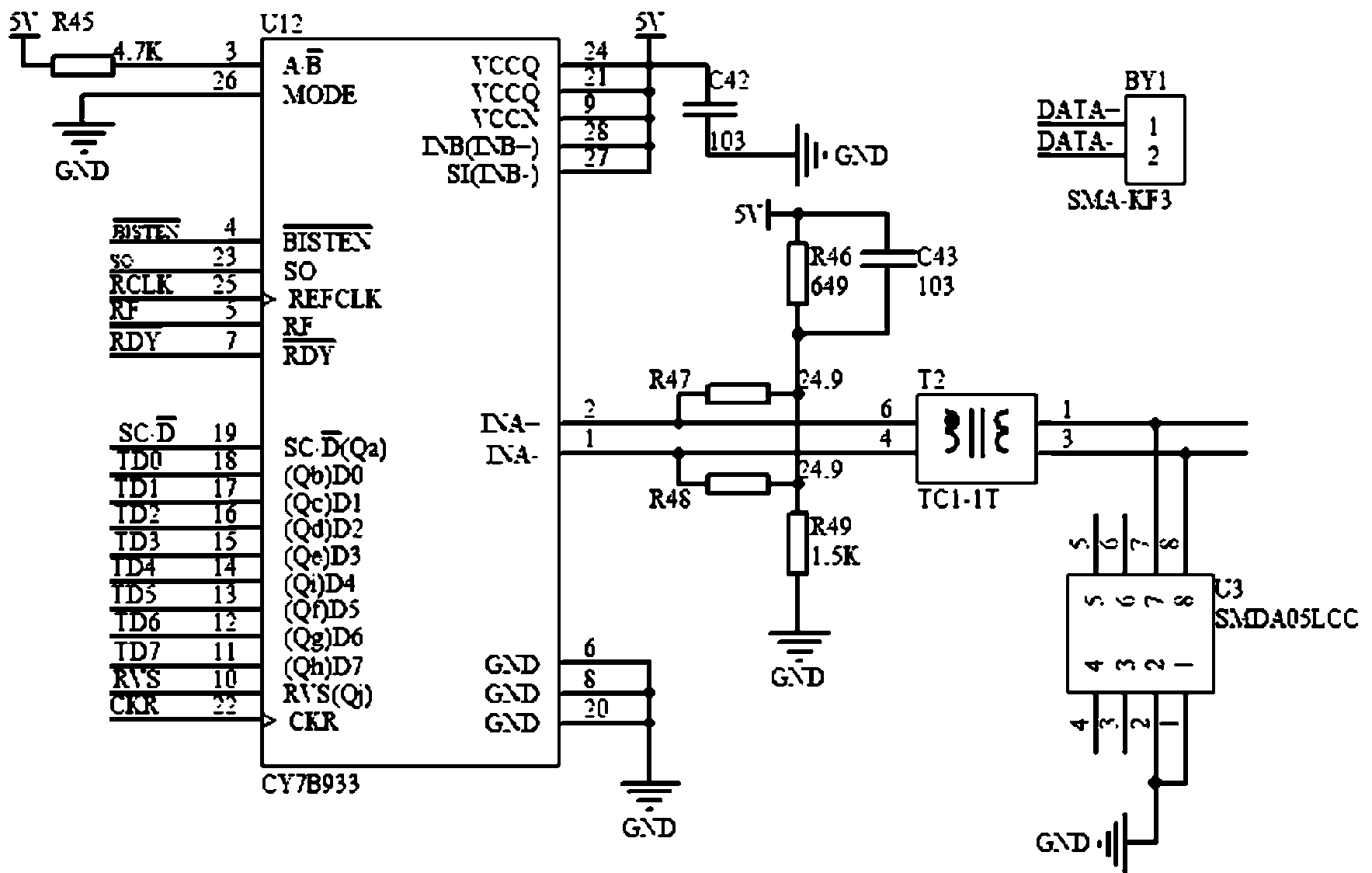

图5为CY7B933接收电路图。HOTLink数据经过200 m同轴电缆传输后由连接器SMA-KF3输入,经过TC1-1T和SMDA05LCC的处理后送至HOTLink数据接收芯片CY7B933;R47和R48为阻抗匹配电阻,其阻值为SFF-50-5同轴电缆特性阻抗的一半,由于25 Ω电阻不是标准阻值电阻,此处选取24.9 Ω电阻代替;R46和R49组成一个分压器,为输入的HOTLink信号提供直流偏置以满足其电平需求[7];同时R46与C43组成一个RC滤波器滤除输入的高噪声信号;R45为上拉电阻,由于本设计数据选择INA±通道输入,故将A/B引脚上拉至5 V。

3 逻辑可靠性设计

在本任务HOTLink信号高速远距离传输中,数据传输的可靠性是判断设计成功与否的最重要的标准[9],本次设计的主控芯片采用了Xilinx公司的6系FPGA——XC6SLX150_3FGG484I。本设计中硬件电路部分选用的CY7B923/933芯片,具有将数据进行8B/10B编解码功能,而传统的8B/10B编码后的数据在传输环境恶劣且传输速率高的情况下会很大程度地增加数据误码率[10]。BCH码是具有纠错能力的循环码,可以随机地纠正多个错误,相较于其他编解码方式因其编解码手续简单、延时小以及实时性高而被广泛地应用于通信领域中[11],本设计结合了8B/10B编解码的直流平衡和BCH编解码的随机纠错的优点,在数据传至CY7B923芯片之前进行BCH编码,可有效地降低数据传输的误码率,极大地增强了其可靠性。

图5 CY7B933接收电路图

3.1 BCH编码设计

本方案中将输入的8 bit数据分为高4 bit和低4 bit数据,先后将高4 bit和低4 bit数据送入(7,4)BCH编码模块中编码,(7,4)BCH码码长为7 bit,包含4 bit信息位和3 bit校验位[12]。4个信息位构成的信息多项式为:

i(x)=i0+i1x+i2x2+i3x3

(1)

在伽罗华域GF(23)上其最小多项式可表示为:

g(x)=x3+x+1

(2)

假设BCH编码后其系统码为:

c(x)=i(x)x3+q(i(x)x3)g(x)

(3)

式(3)中,q(i(x)x3)g(x)表示i(x)x3除以g(x)后的余数多项式。因而校验多项式可表示为:

r(x)=x3i(x)modg(x)=r0+r1x+r2x2

(4)

将式(4)代入式(3),可得编码后系统码多项式为:

c(x)=x3i(x)+r(x)=x3i(x)+x3i(x)modg(x)

(5)

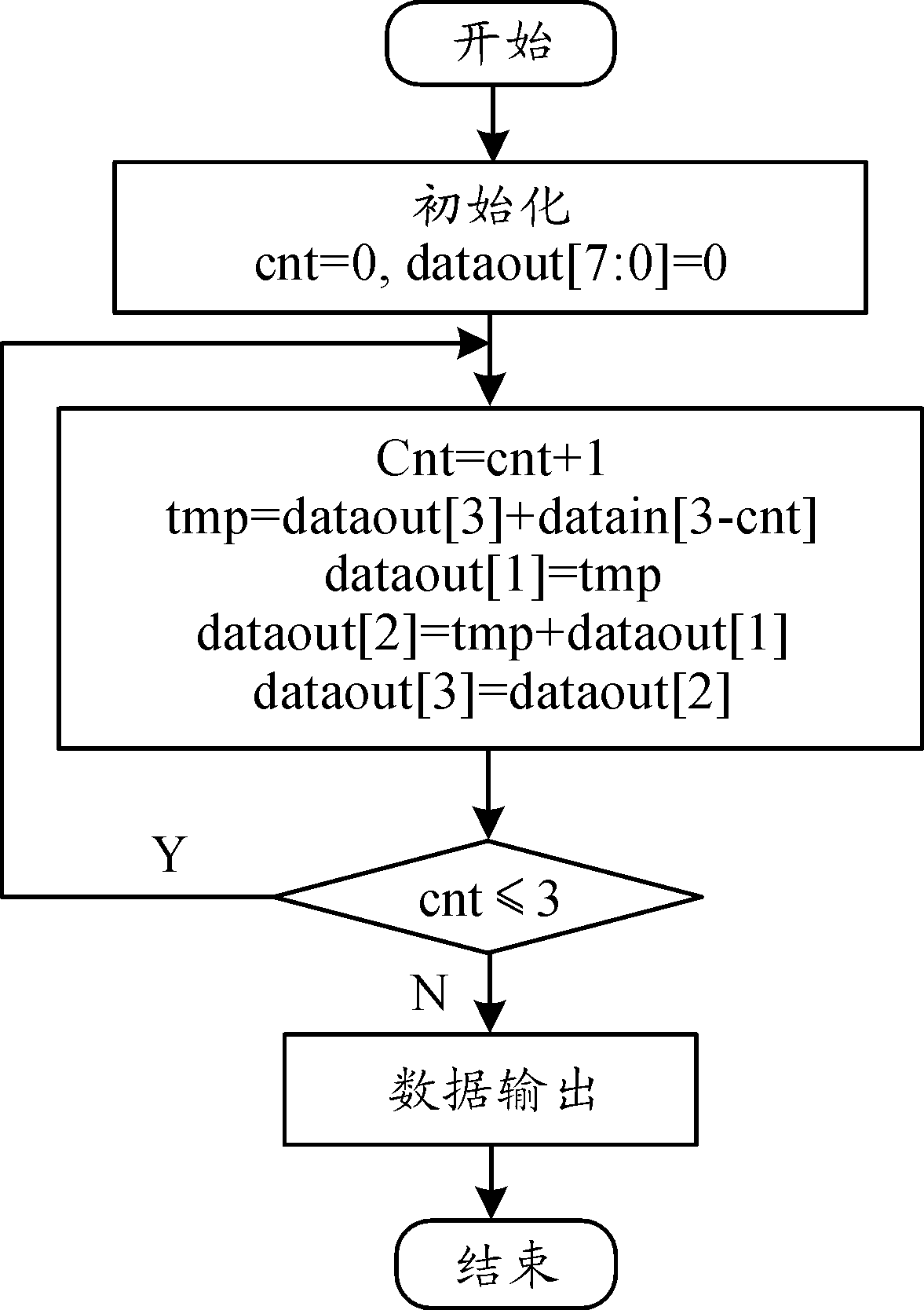

按照此方法得到的系统码中,将4 bit信息左移3 bit,然后除以g(x),即可得到3 bit余项,即为3 bit校验位。由于BCH码为循环码,因此其编码电路可由如图6所示编码电路图中的线性串行移位寄存器所实现。

图6 (7,4)BCH编码电路图

4 bit信息位依次进入BCH编码电路后,经过3个时钟周期延迟,依次输出3 bit校验位,并在最后一位补0,以保证发出的信号为8 bit信号。(7,4)BCH编码流程如图7所示。

图7 (7,4)BCH编码流程框图

BCH编码结束后将8bit数据通过FPGA的I/O口输出至CY7B923的D0~D7端口,随后进行8B/10B编码并发出。

3.2 BCH译码设计

FPGA接收到CY7B933解码后的8 bit码,然后进行(7,4)BCH译码,译码过程主要分为以下步骤:

步骤1 求接收到的BCH码余式,将3.1节式(2)中g(x)作为除式,产生余式定义为“部分校正子”[13];

步骤2 根据式(5)中部分校正子构造错误位置方程,该方程式的根即为错误位置;

步骤3 求解错误位置方程式的根并进行纠错。

定义部分校正子为S(x),接收到的BCH码多项式为R(x),错误图样多项式为E(x),译码后多项式为C(x)[14],则有如下关系式:

R(x)=C(x)+E(x)

(6)

C(x)modg(x)=0

(7)

S(x)=R(x)modg(x)=E(x)modg(x)

(8)

部分校正子可以采用如图8所示译码电路图中的除法电路计算得到,然后根据部分校正子所构造的错误位置方程的根进行纠错。

图8 (7,4)BCH译码电路图

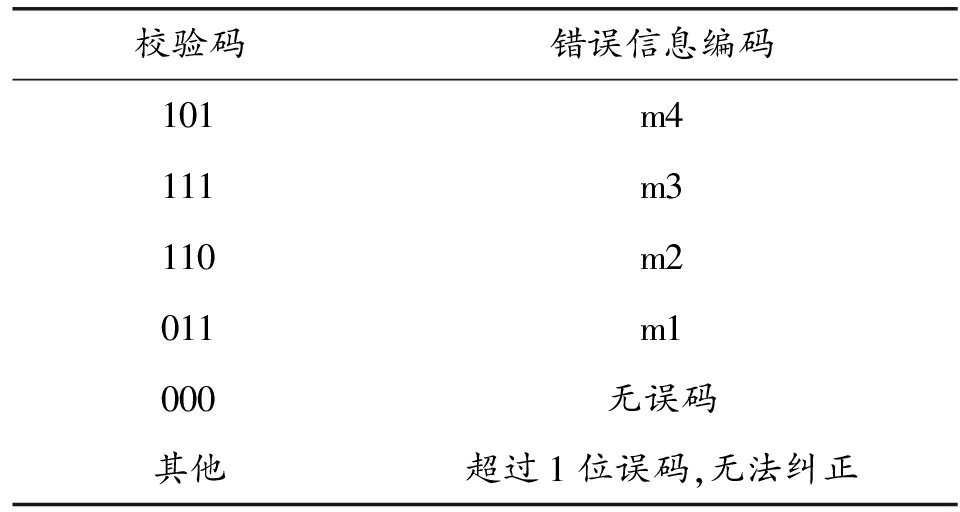

8 bit码去掉末位0之后从高位到低位依次进入BCH译码电路,经过3个时钟周期延迟,依次输出3 bit校验码,并根据如表1所示的校验码与错误信息编码对应关系表进行误码纠正。

4 可靠性结果验证

为了验证本次设计的可靠性,采用数据采集编码器、地面测试台与上位机共同搭建的测试系统。地面测试台与数据采集编码器之间的数据传输采用了200 m的同轴电缆作为传输介质。测试中将数据采集编码器与同轴电缆放置于60 ℃高温环境并向同轴电缆中注入脉冲激励作为干扰用于模拟任务环境,采用的数据帧结构如图9所示,其中“96 14 6F 14 6F”为数据帧包头,“00 00 00 00~00 00 00 09”为包计数,数据为00~59的递增数。

表1 校验码与错误信息编码对应关系

校验码错误信息编码101m4111m3110m2011m1000无误码其他超过1位误码,无法纠正

图9 数据帧结构

通过FPGA程序控制HOTLink串行数据的传输速率,进行如下误码率的测试,不同传输速率的情况下各测试50次,每次测试数据为8 GB,测试结果见表2。

表2 测试结果

传输速率/(Mbit·s-1)加入BCH编码前平均误码率/%加入BCH编码后平均误码率/%40001200.0002102000.0017202800.012950330频繁误码0

根据测试结果可知,硬件电路可以保证以40 Mbit/s的传输速率在200 m的同轴电缆中无误码传输,但随着传输速率的增加,误码率会越来越大,远不及测试任务要求。但在FPGA程序中加入BCH编解码后,可以有效地降低数据误码率,从而满足任务对于以330 Mbit/s传输速率在200 m的远距离传输的要求。

5 结论

本文针对任务要求以及测试环境,在硬件上设计了CY7B923和CY7B933的外围电路,在逻辑设计中增加了可纠错的BCH码优化方案,极大地增强了传输链路的可靠性。通过大量的测试实验,验证了本设计中HOTLink数据在60 ℃高温且有脉冲激励干扰情况下可以实现330 Mbit/s传输速率在200 m的同轴电缆上无误码传输,满足测试任务要求。

[1] 王小阳,章宇栋,童峰.采用多通道信道均衡的调频水声语音通信[J].兵器装备工程学报,2019,40(1):168-172.

[2] 陈志纯.成像声呐信号源与信号采集系统设计实现[D].哈尔滨:哈尔滨工程大学,2011.

[3] 刘佳宁,文丰,王淑琴,等.基于HOTLink的高可靠性长线传输设计[J].电子器件,2017,40(5):1209-1213.

[4] 王圣豹.多波束参量阵浅地层刨面仪测深分机接收与采集电路设计[D].哈尔滨:哈尔滨工程大学,2015.

[5] CYPRESS.CY7B923/CY7B933 HOTLink® Transmitter/Receiver[Z].2014.

[6] 高速串行数据发送接收芯片CY7B923/933的原理及应用设计[J].地质装备,2015,16(2):27-30.

[7] CYPRESS.HOTLink® Design Consideration[Z].2014.

[8] 陆波.多波束测深仪多通道接收机及采集系统设计[D].哈尔滨:哈尔滨工程大学,2012.

[9] 赵阳刚,郭涛,黄玉岗.基于FPGA和LVDS的弹载数据回读系统设计[J].电子器件,2017,40(1):113-117.

[10] 张平.基于FPGA的高速8B/10B编解码电路设计[D].合肥:安徽大学,2016.

[11] 于立波.高速BCH编码器的软件与硬件实现[D].成都:电子科技大学,2012.

[12] 于立波.并行BCH编码器的设计与实现[D].南京:南京大学,2018.

[13] 王方,周璐,张正璠.8B/10B编码器新型算法结构的设计与实现[J].微电子学与计算机,2016,33(10):151-154,158.

[14] 张磊.基于纠错技术的高速串行编解码器研究与设计[D].合肥:合肥工业大学,2011.