在炮口弹丸初速、破片测速的测试手段中,靶网测速是较为成熟的手段[1]。靶网又根据原理不同分通靶与断靶。通常而言,通靶相较断靶容易制作,但仅可触发一次,常用于弹丸测速项目;断靶根据着靶点不同可进行多次触发,更适用于破片测速场合中。但现有靶网测试常有以下缺陷:

1)针对两种靶网需设计不同的测速仪器,现有破片测速系统和炮口测速系统各行其是,且受爆炸产生的电磁干扰影响[2];

2)目前主要采用220 V交流供电,还需配置油机和掩体,移动不便,现场试验工作效率低[3]。

针对以上靶网测试法存在的不足,设计了一种通/断靶皆可触发的多通道便携式测速系统。该系统以FPGA为控制核心,采用单片高速AD转换器,以NAND FLASH作为最终存储单元,结构小巧,操作简单,可提高现场靶场测试的灵活性以及测速数据的可靠性。

1 系统原理设计

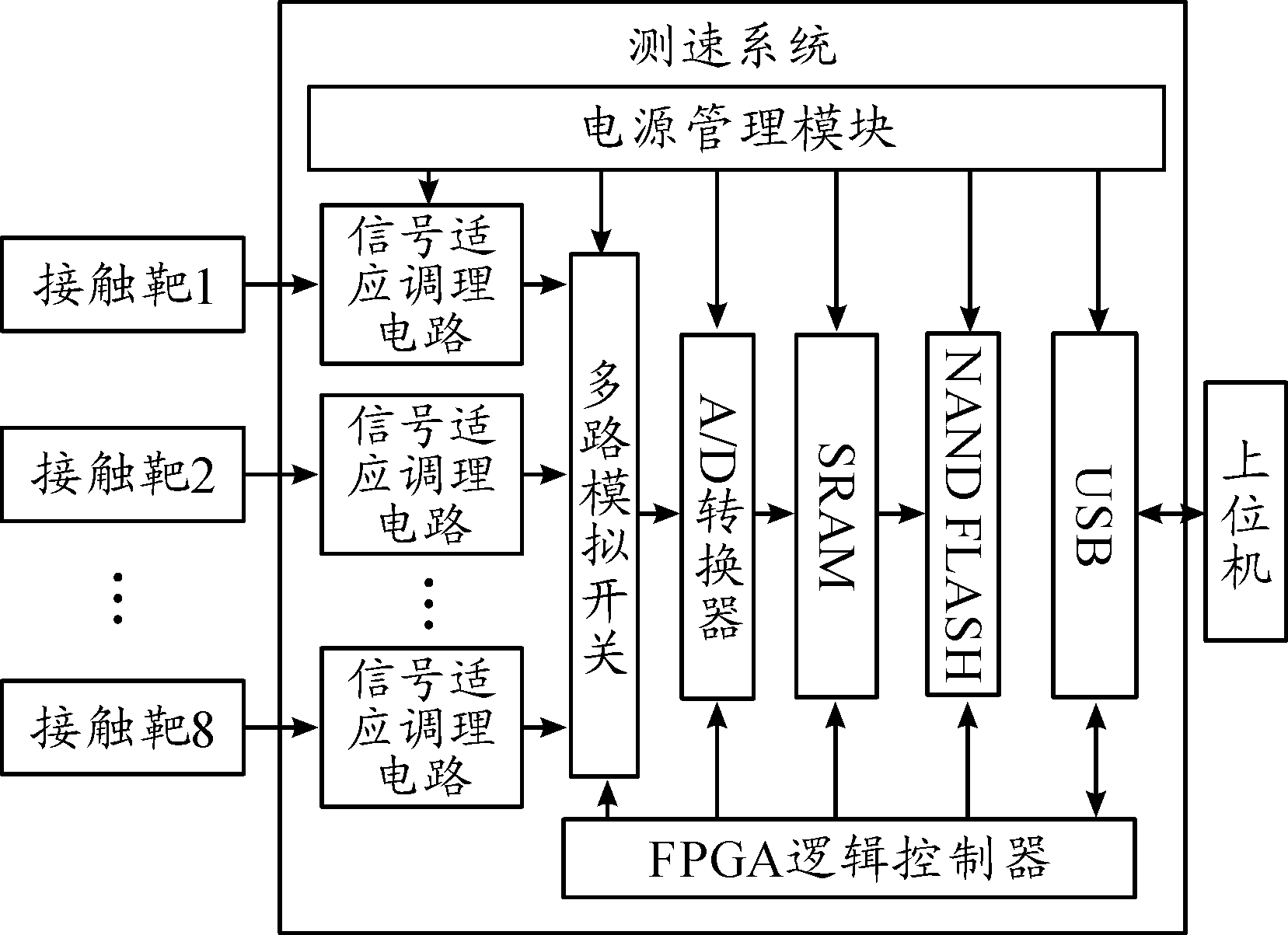

该测速系统在综合考虑便携性和系统可靠性的基础上,采用存储测试原理设计[4],即系统对破片或弹丸过靶产生的信号进行调理并存储,在实验结束后进行回读分析的测试方法。系统设计原理如图1所示,其设计思路如下:

1)测速系统共分8通道,每通道通过引线接靶,系统上电后,信号自适应调理电路可迅速识别靶类别并调整触发模式。系统触发后,信号自适应电路仅输出对应调理后的靶线通或靶线断信号。

2)该系统脱离现有多通道存储式测速系统的多控制器+多AD转换器+多片存储器的架构,以高速AD转换器+多路复用器架构实现信号采集[5-6],采用FPGA为控制核心。此架构可在信号完整度以及采样精度得以保证的前提下较大程度地减小系统体积,降低功耗。

图1 系统设计原理框图

系统工作过程:试验前,根据爆炸当量和各测点相对于爆心的距离对测试系统进行相关工作参数的设定,包括存储长度、负延时长度等,系统对设定好的工作参数具有记忆功能。系统上电后进入循环采样阶段,战斗部起爆后,触靶信号使系统触发,各通道信号在同一时基下开始记录,将有效数据保存到存储器中;存储完成后通过USB接口进行数据读取,利用上位机对测试数据进行显示处理。

2 关键技术研究

2.1 通/断靶自适应调理电路设计

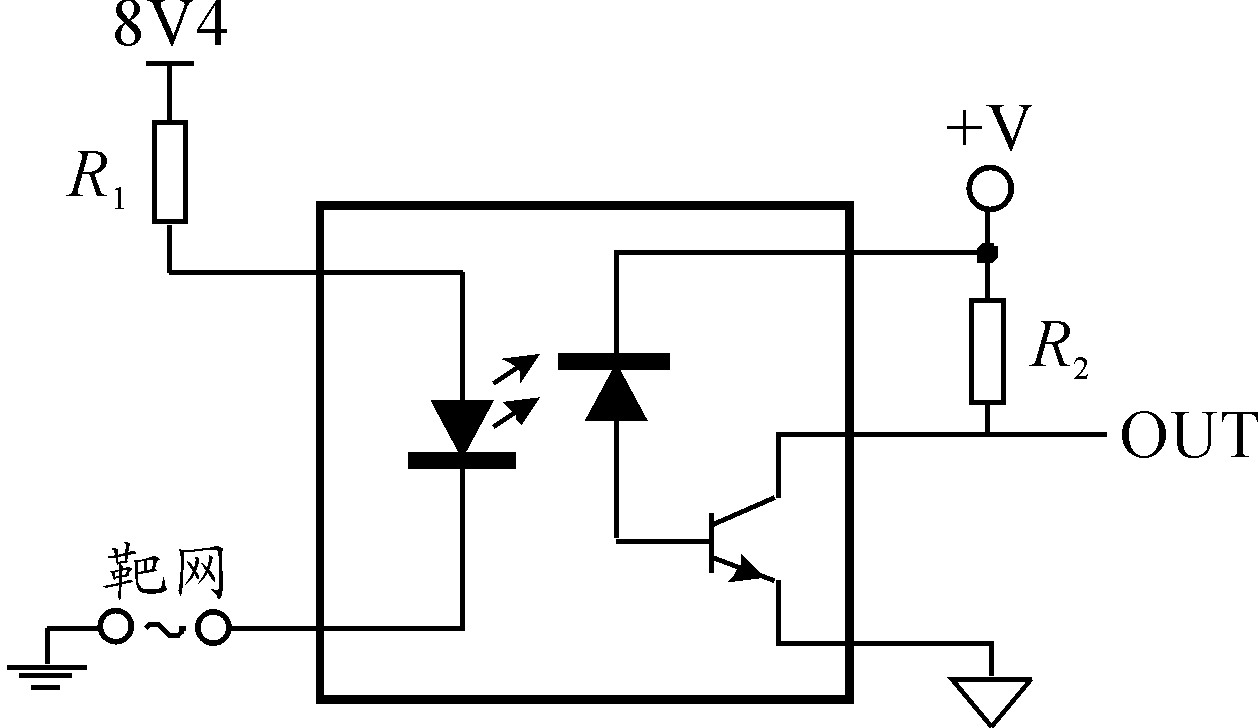

2.1.1 基于高速逻辑光耦的信号转换电路

在爆炸威力实验中,爆炸产物高速飞散并与周围空气介质发生剧烈摩擦和碰撞,最终会在周围空气中形成等离子体。这些带电离子会通过触发线以及梳状靶耦合进测速仪,引起强烈的电磁干扰。在以往的测试实践中,采集的数据可以反映出这一现象的存在。如果不采取信号隔离和抗干扰措施,杂乱的干扰信号轻则影响有效信号的分析,强电磁干扰甚至会导致系统瞬间崩溃。针对以上问题,本系统采用高速逻辑光耦实现对过靶信号的隔离,使信号的输入端和采集端没有电气连接[7],且在隔离两端采用不同的接地点,切断“地”干扰的传播途径,彻底实现了两端信号的电气隔离。高速逻辑光耦抑制干扰信号的同时还可将靶网的通断信号转换成对应的极性信号。其转换电路图如图2。

图2 靶网信号转换电路图

当靶网的靶线导通时,光耦内部发光二极管发光,反向偏置的光敏二极管受光照后导通,经输出三极管反向后光耦输出低电平;当靶线断开时,三极管输入电流小于触发阈值,光耦输出高电平。即光耦输出可实时反映出当前靶线状态,在对于给定的某类型靶(通靶或者断靶),弹丸或者破片过靶前后产生的信号极性是不同的。这个信号本身是需要记录的对象,同时也可以作为靶类型识别的依据。

2.1.2 自适应信号发生调理电路

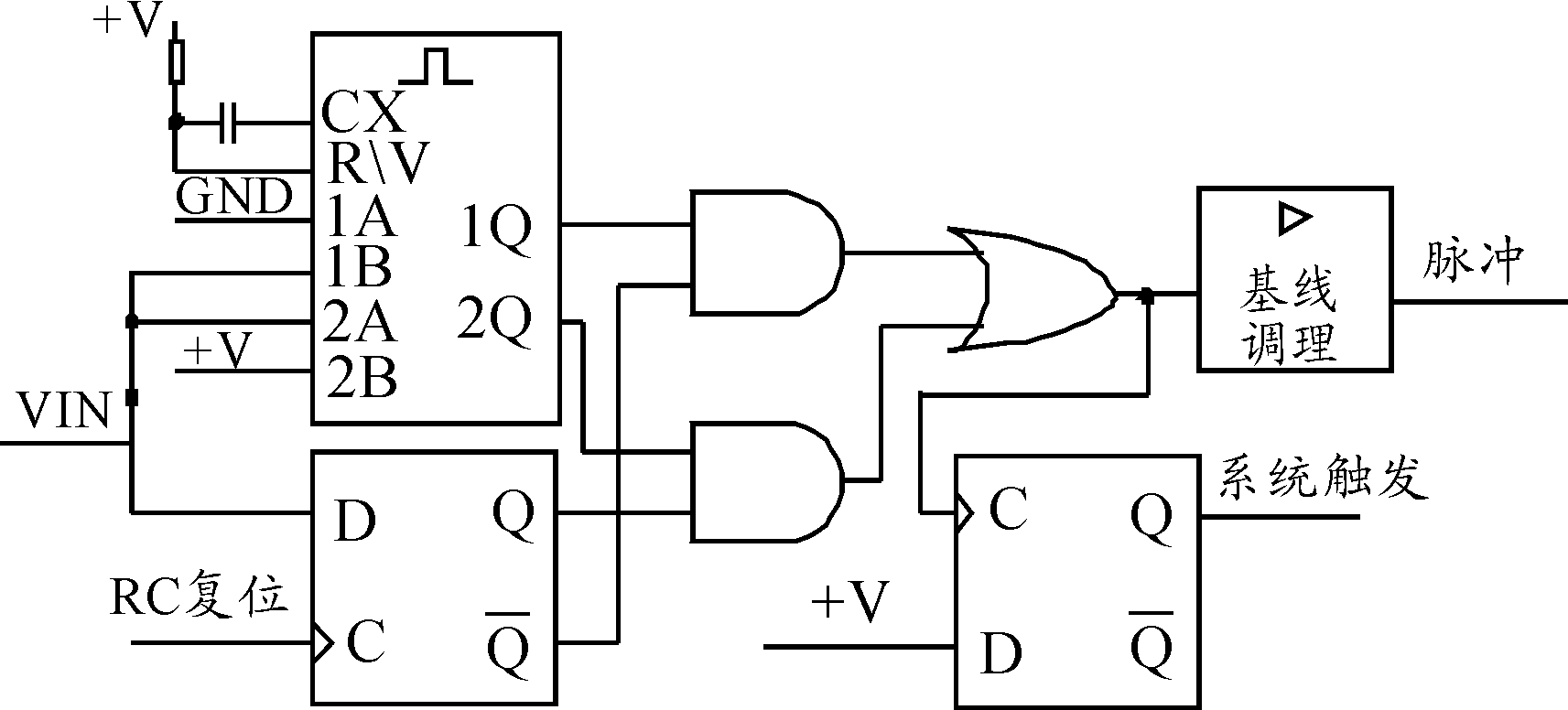

为准确识别当前靶类别、屏蔽非当前靶的信号且将有效信号调理至合适的范围以便后续电路处理,系统采用简单逻辑器件如D触发器、单稳态触发器等完成对光耦输出信号的硬件识别、屏蔽、调幅,并将弹丸/破片过靶的边沿信号转换成脉宽较小的脉冲信号。自适应信号发生调理电路如图3所示。

图3 自适应信号发生调理电路图

当外部引线接好靶网后,系统上电,D触发器经RC电路高复位识别未触发的靶信号。若当前靶网为通靶,调理电路仅输出靶线被打断的对应脉冲;同理,若当前靶为断靶,调理电路仅输出靶线导通的对应脉冲。在该电路中,单稳态触发器在输入信号极性发生变化时产生并输出脉冲,D触发器、逻辑与门和或门则根据靶网初始状态对该脉冲选通输出。

另一方面或门输出的脉冲信号需要经过基线调整和信号缩比电路才可以由ADC采样,同时该脉冲信号经触发器输出系统内触发信号,使测速系统各通道的数据开始记录。

2.2 基于FPGA的采集存储逻辑设计

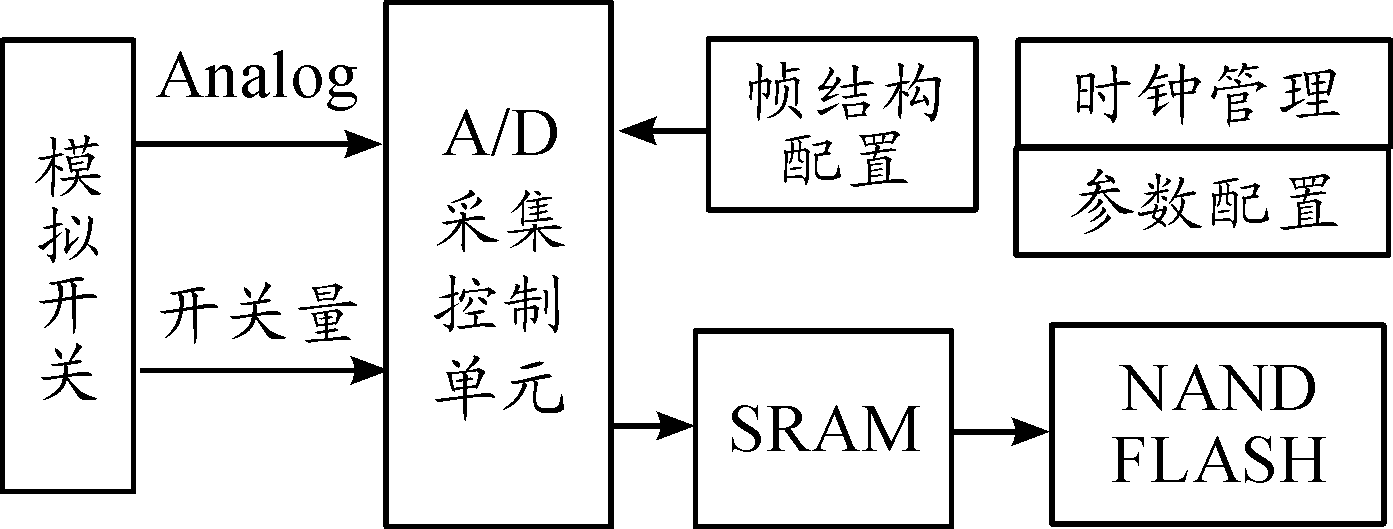

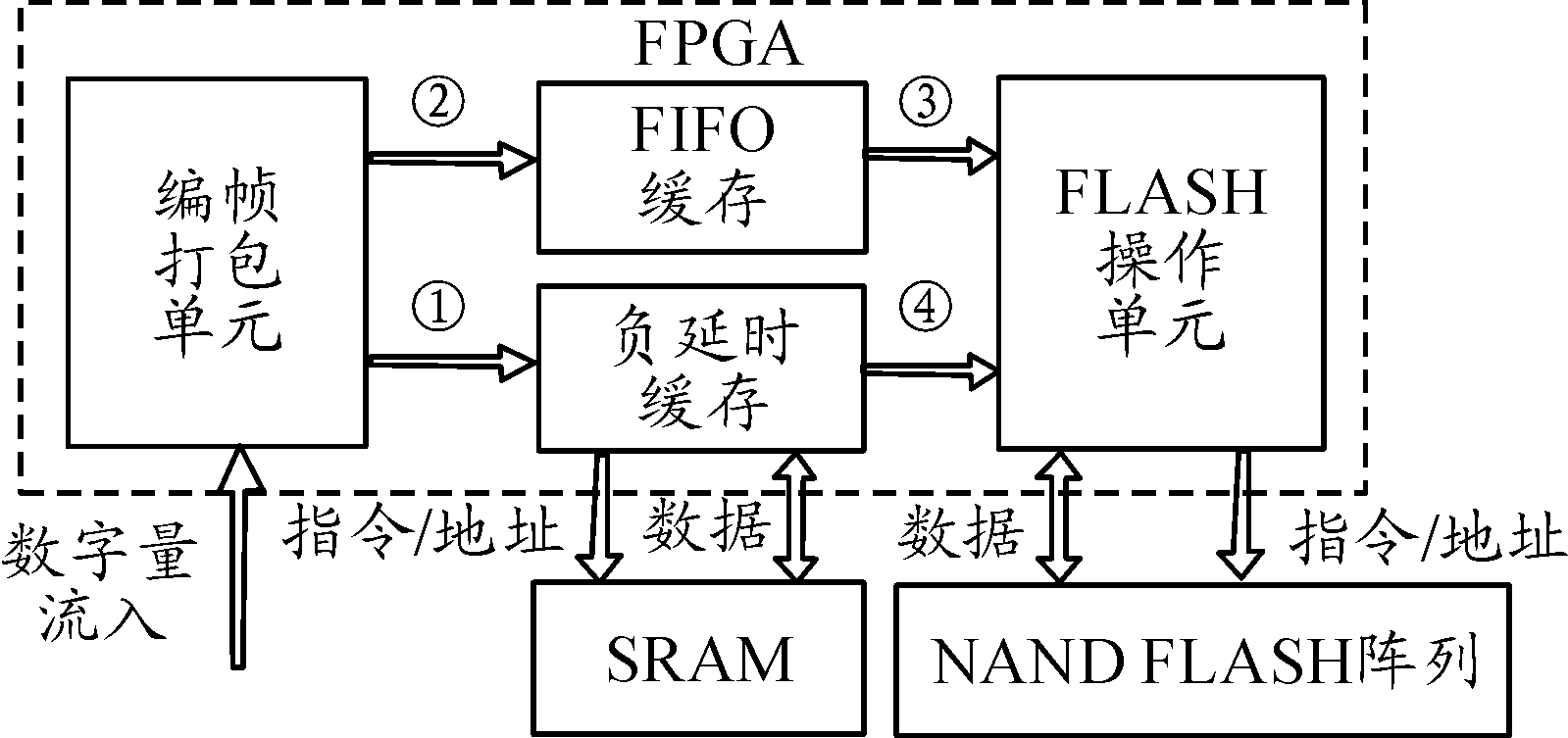

FPGA是现场可编辑门阵列,相较其他处理器,FPGA具有并行处理数据的优势,更适用于多通道、数据吞吐量高的场合中[8]。本系统采用FPGA作为主控单元,主要实现各通道数据的采集、编帧打包、缓冲、存储等功能。基于FPGA的采集存储逻辑框图如图4。

图4 FPGA控制逻辑框图

2.2.1 多路模拟开关+单片AD架构逻辑设计

多路模拟开关的选取主要考虑以下指标:通道数量、导通电阻、切换速度和芯片电源电压范围等[9]。系统选用ADI公司的8选1高速模拟开关ADG708,其导通电阻为3,电阻平坦度为0.5,切换速度达14 ns,电源电压范围为1.8~5.5 V,满足设计要求。FPGA逻辑电平的上升和下降时间都很短,可实现时序逻辑的精准控制[10],ADG708可在FPGA控制下实现8路通道的快速切换。其中每一路都唯一对应模拟开关的一个通道,通过控制ADG708的通道地址“A0-A3”即可选通8路模拟通道的某一个。

根据靶网产生的脉冲信号的采样需求,各通道采样率需达到1 MHz,所以8路总采样率为8 MHz,本系统选用ADI公司的高性能12位模数转换器AD9220,其最高采样率达10 Msps。它采用特有的四级流水结构和错误修正,可保证在整个工作温度内没有误码,适合常规靶场爆炸包括炮口测速的高温恶劣环境。

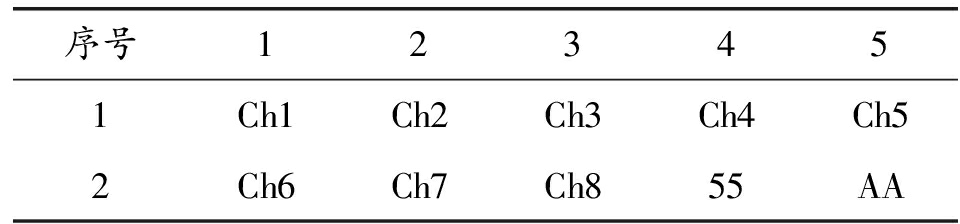

为方便时序逻辑的设计和对信号采样率的控制,将采样的数据帧设置为固定格式,数据帧结构如表1所示。因各通道采样率均需满足1MHz,故每个采样点采样频率取1 MHz。在帧尾增加帧结束标志55、AA,便于上位机回读数据时对数据是否发生丢帧和误帧进行检测。该帧结构保证各采样点均匀采样,使多路数据有序写入存储器,且在上位机读取数据后便于区分各路模拟信号的量化数据。

表1 数据帧结构

序号123451Ch1Ch2Ch3Ch4Ch52Ch6Ch7Ch855AA

2.2.2 存储逻辑设计

与其他存储介质相比,NAND FLASH以其容量大、体积小、掉电数据不丢失且功耗低的特点,成为当今存储元件的首选。存储式记录仪不可避免会需要有效记录波前信号,即负延时功能。但是NAND FLASH自身的存储结构决定了存储数据之前需要花费ms级的擦除时间,且测试数据也不能连续写入,降低了FLASH总体写入速度,并不适用于瞬态信号的快速存储。若采用多片FLASH进行流水操作来填补擦除时间的数据,则造成FLASH资源浪费和增加编程难度,因此选用SRAM+FLASH阵列来实现系统存储逻辑[11]。整个数据处理和存储流程如图5所示,其中采用SRAM作为负延时缓存单元;采用FPGA内部IP核例化FIFO作为触发后数据的缓存单元;采用了两片FLASH作为最终存储单元。

图5 存储逻辑设计流程框图

存储流程共分四步:第一步,未触发时,FPGA根据需要设定负延时长度并在FLASH内部留出同等的地址空间。此时FPGA可快速的将数据写入SRAM,进行负延时操作;第二步,触发信号到来后,在SRAM写入16 Byte负延时标识信号,并将接下来AD采集的数据通过FPGA内部FIFO缓存;第三步将FIFO数据取出,写入FLASH单元;第四步采集完成后,将SRAM中数据取出,写进预留的FLASH空间。如此操作,就可将全部的数据写入最终存储单元FLASH中。其中SRAM仅作为负延时缓存单元,触发后的数据则由FIFO缓存,避免采集期间同时对SRAM和FLASH进行控制,操作较为简洁,且利用FIFO有助于提高代码稳定性和效率。

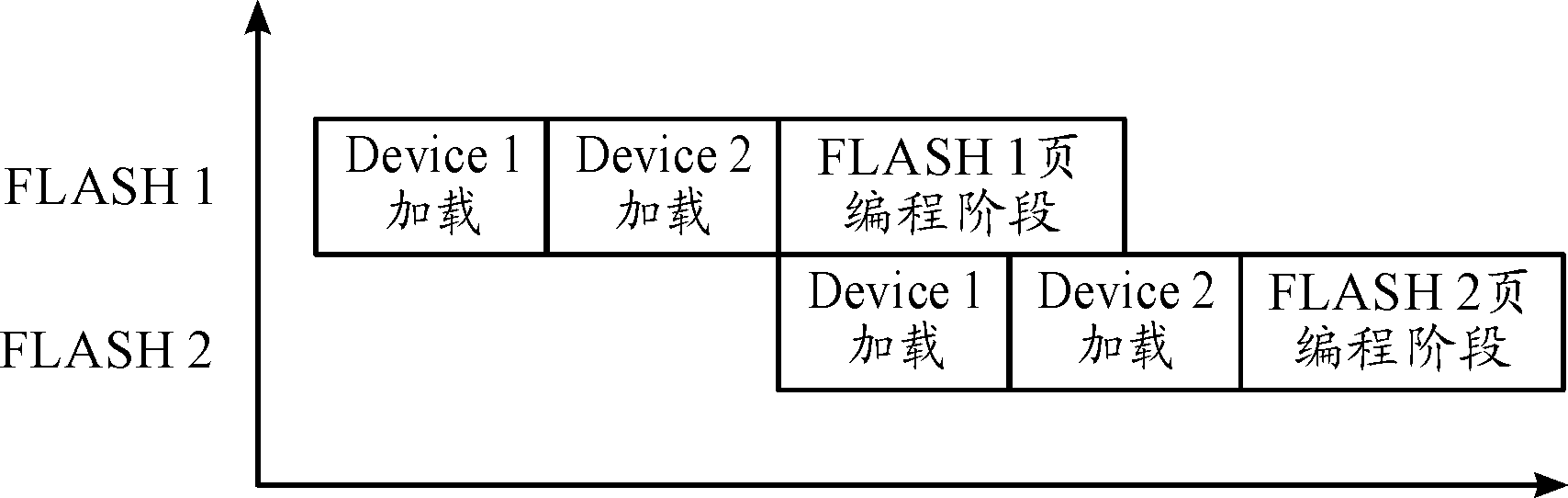

本系统总采样率8 MHz,分辨率为12位,理论数据写入速率为14 MB/s。存储介质选取镁光公司的MT29F8G08ABA,其页编程时间tPROG为200~600 μs,页容量4 096 Byte。按照图5逻辑,若用单片FLASH的交替双平面操作模式,数据写入速率在9.9~19.8 MB/s之间。为保证数据可靠性,最终采用双片FLASH片内交叉片外流水操作[12]。双片FLASH流水线操作如图6所示。

图6 双片FLASH流水操作示意图

双片FLASH流水存储本质为循环利用第二片FLASH的加载时间填补当前FLASH的页编程繁忙时间,其理论写入速率为15.84~26.2 MB/s,满足设计需要。

3 同步性测试和实验验证

3.1 多通道同步性测试

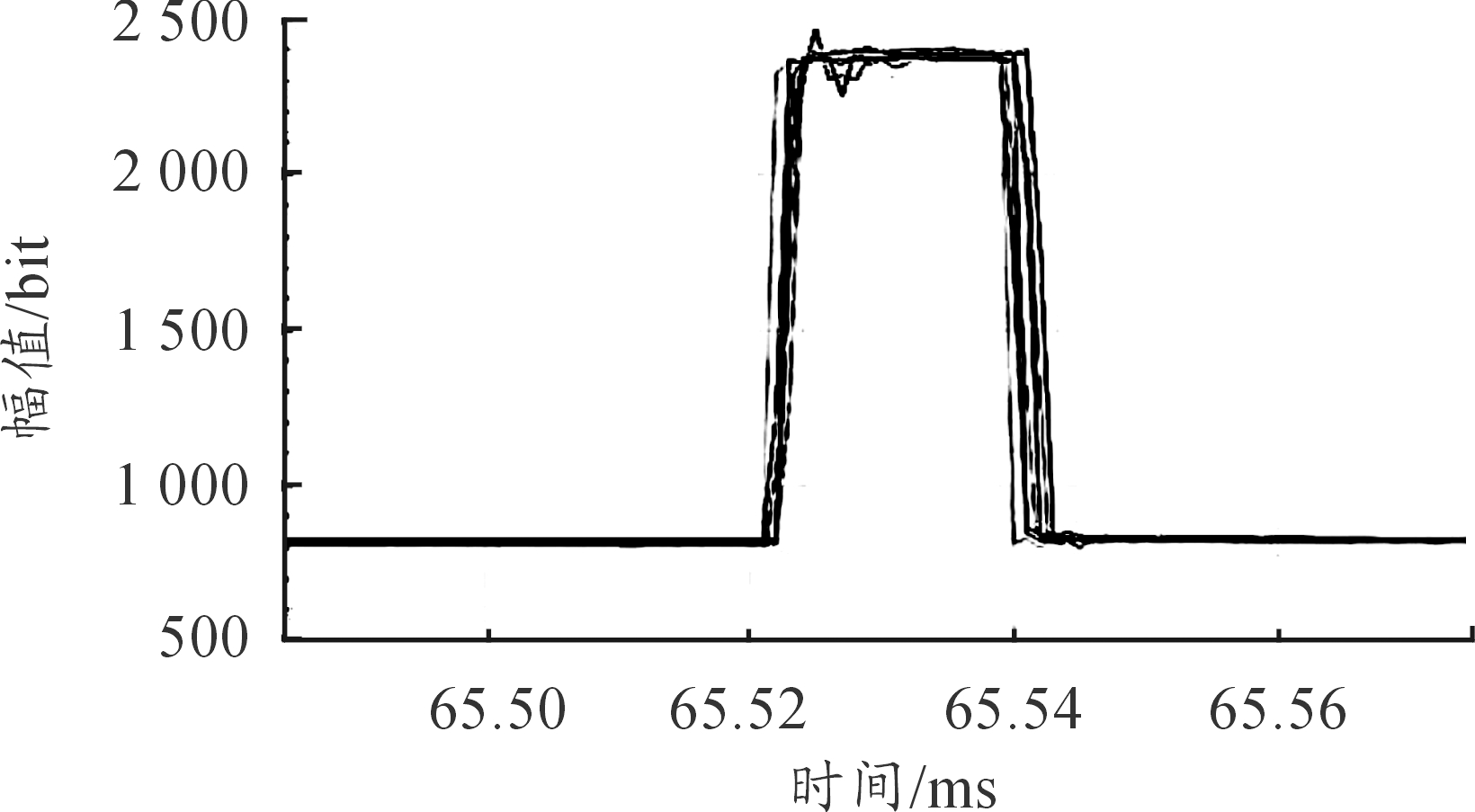

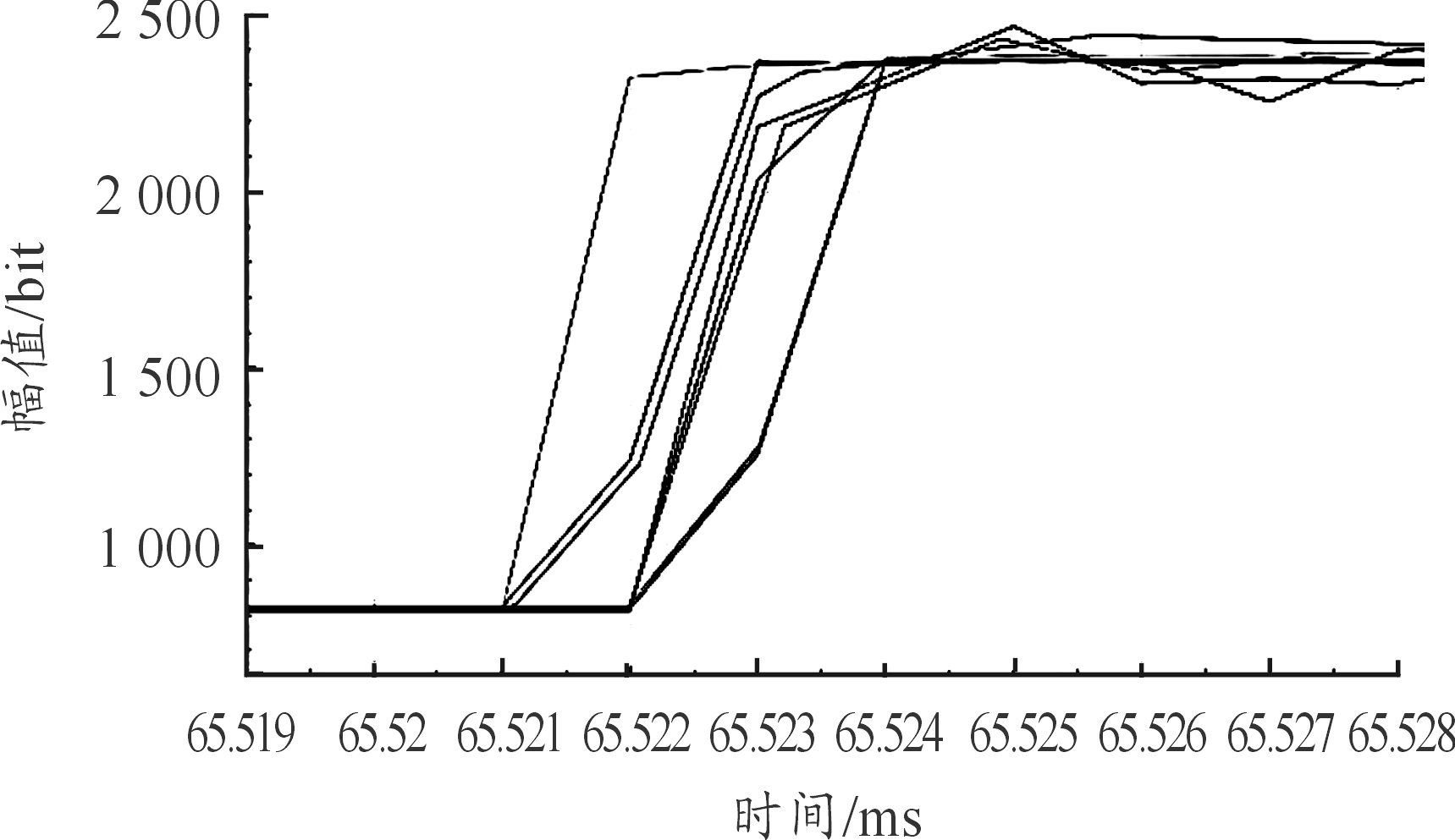

多通道同步性测试是为了测试在同一时基下各通道的同步性误差,同时也是对系统原理以及PCB等设计的综合考量。在同步性测试中,用系统8通道同时采集同一断靶信号,图7为8通道过靶波形,图8为波形放大之后的起始时刻,可知:多通道同步性误差仅为1 μs,这在使用靶网的实验场合中对数据的影响可忽略不计。

图7 多通道过靶波形

图8 多通道同步性波形(放大)

3.2 系统性能试验验证

本系统已在多次靶场弹丸破片测速现场试验中得到成功应用,验证了其可靠性和便捷性。在某次炮口初速测试试验中,通靶安装在离炮口50 m的弹道支架上,靶距4 m,测速系统通过长引线接靶,并有高精度光幕测速仪记录弹丸瞬态速度。图9为弹丸过靶后的测速现场。

图9 某型炮弹丸初速测试现场

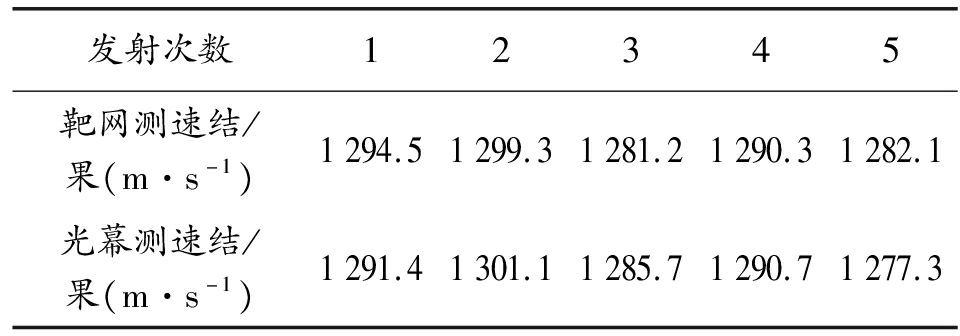

多次试验测量数据如表2所示,从表中可以看出本系统与高精度光幕测速仪测速的结果基本一致。

实验证明,按上述原理设计的测速装置和测试方法行之有效,多通道测速系统在野外环境下操作简单灵活、数据稳定可靠,可满足常规靶场的测速需求。

表2 某型炮多发试验测量数据

发射次数12345靶网测速结/果(m·s-1)1294.51299.31281.21290.31282.1光幕测速结/果(m·s-1)1291.41301.11285.71290.71277.3

4 结论

本系统采用记录破片过靶波形的方法,能够清晰再现破片穿靶过程,极大地提高了破片识别的正确率;信号极性可自动识别,不需人员干预,实现了一机两用,使用方式灵活便携;测试人员可根据具体测试任务进行通道数的灵活选择和系统工作参数的可编程设置,上位机选取特征点简单,数据处理准确高效,满足对不同弹丸破片的测试需求,为各类弹丸破片及破片速度评估提供了一种有效可靠的测试手段。

[1] 许地鑫.靶网测试法在破片初速测试中的应用[J]现代测量与实验室管理,2012,20(1):13-15,18.

[2] 李丽萍,孔德仁,易春林,等.战斗部破片速度测量方法综述[J].测控技术,2014,33(11):5-7,13.

[3] 李丽萍.破片战斗部毁伤威力测试关键技术研究[D].南京:南京理工大学,2017.

[4] 马铁华,祖静.冲击波超压存储测试技术研究[J].仪器仪表学报,2004(S1):134-135,146.

[5] 刘宏伟.基于VXI总线虚拟仪器技术的破片测速系统研制与应用[J].中国设备工程,2018(24):89-90.

[6] 赵爱明,刘卓夫,郭环球.多路复用器建立时间及其在伺服控制电路中应用[J].电测与表,2016,53(15):47-52.

[7] 魏鹏,赵河明,张志.一种基于FPGA的全隔离炮口测速方法[J].信息技术与信息化,2013(5):102-105.

[8] 王建中,杨璐.高速实时系统数据采集与传输[J].计算机科学,2016,43(S2):604-606.

[9] 陶海军,张一鸣,曾志辉.基于AD7606的多通道数据采集系统设计[J].工矿自动化,2013,39(12):110-113.

[10] 张传民.某弹载多通道数据采集系统的研究与设计[D].太原:中北大学,2015.

[11] 曹勋,赵冬娥,李致成,张斌.提高测速系统存储速率及可靠性的方法[J].电子器件,2016,39(1):152-155.

[12] 高阳.弹载数字图像采集系统研究[D].太原:中北大学,2017.