近些年,全球数据中心网络[1]的流量保持超高速增长。根据思科公司的技术白皮书,在所有增长率方面,数据中心内部流量占77%。随着数据中心内交换流量的不断增加,亟需实现数据中心网络更低延迟的互连结构。

传统的多层拓扑结构正在被扁平化的全对分带宽架构所取代[2],如叶脊式架构,这种拓扑结构支持扩展到更高的端口数,同时提供完整的对分带宽。由于所有路径都是等距的且长度最短,因此,能够实现较低的机架间延迟[3]。然而,带宽扩展受到电子芯片上高速信号引脚数量的限制[4]。利用波分复用(WDM)技术的光交换网络能够有效提高传输容量的量级,突破对分带宽的瓶颈,例如c-Through[5]、ROSA[6]等,这些技术方案可以增加数据中心网络的对分带宽,降低成本和延迟。在控制平面方面,使用复杂的调度算法估计流量需求可以提高线路利用率,但会进一步增加交换路径确认信令所造成的双向延迟和处理开销。

光交换机能够处理迅速变换的突发流量,数据包被转发到交换机且不用等待确认信令,并有效预测交换路径。但难题是如何建立能够在分组时标上操作的控制平面。为了避免对全局调度的需求,有些方案[7-8]使用波长路由的光网络架构。但该类方案的缺点是显著增加光学元件数量,尤其是需要使用成本较高的波长转换设备。此外,还有基于FPGA的集中式控制平面[9],支持以75 ns的端到端延迟进行光分组交换。

本文设计了一种高速的控制平面,在FPGA板上实施了该控制平面,确认了端到端延迟和控制平面作用,并分析了实现最小调度延迟的难点。实验表明:通过高速调度和在并行WDM信道上的预测性分组传输,实现了纳秒级的分组交换。此外,针对交换机调度器提出了一个高度并行化输出端口分配电路设计,并将该设计实施于同一块FPGA板上作为实验调度器,以量化其对调度器延迟和可扩展性的提升。

1 设计概述

本文提出的系统方法是基于带电子缓冲器的纳秒级可重构N×N光交换机,电子缓冲器作为输入端口处的先入先出(FIFO)队列而实现。通过与交换机位于同处的电子调度器进行交换机配置。在交换机输入处实施缓冲器能够降低端到端延迟,并避免数据包丢失。

1.1 控制平面设计

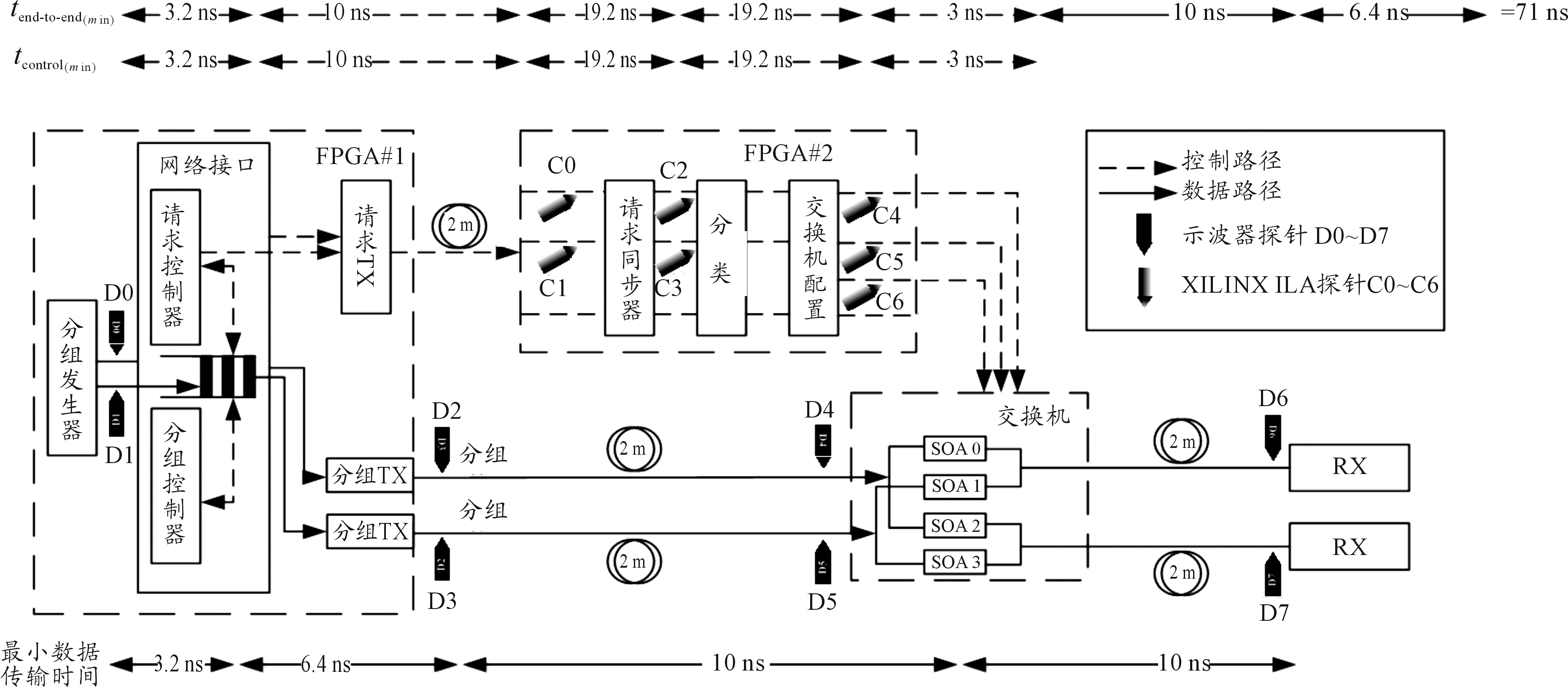

本文设计的控制平面如图1所示,包括两个FPGA板,由分立光学元件组成的一个2×2纵横式光交换机。FPGA#1表示服务器侧的网络接口,以时钟周期Ttx运行;FPGA#2表示位于交换机的调度器,以时钟周期Tscheduler运行。控制平面在两个FPGA板上扩展;包括网络接口中的请求控制器和包控制器,以及调度器电路。示波器探针D0~D7放置于数据路径上。Xilinx集成逻辑分析仪(ILA)探针C0~06在调度器FPGA板上。

图1 控制平面示意图

控制平面的几个重要概念如下:

1) 请求生成。请求控制器读取HOLO包的目的地,并生成请求,耗时1个网络接口时钟周期(Ttx)。

2) 电缆传播延迟。将带外数据传输至调度器,耗时tcable,该耗时由服务器和交换器之间的电缆延迟决定。请求中仅包含目的地输出端口和1个有效位,因此可使用并行电连接进行高效传输。

3) 请求同步化。实验演示中,本文假定网络接口和调度器是异步的(符合当前的商用系统)。请求同步器最坏情况下的延迟(当请求在调度器时钟边沿之后稍晚到达时)为2个Tscheduler。

4) 分配。根据当前交换路径和新请求来确定最优交换配置。分类耗时1个Tscheduler。

5) 交换机配置控制。添加由分配电路制定的新授权,并移除过期授权。新授权用于生成交换配置,包括交换机缓冲器的允许读取信号。任何未授权信号均会转化为交换机处数据包缓冲的允许写入信号[10]。该组件耗时1个Tscheduler加上交换机配置时长tswitch。

本文通过分析控制平面设计的组件,并量化各个组件的延迟,可知总控制延迟随网络接口和调度器的时钟周期Ttx和Tscheduler而变化,最小控制平面延迟是确定的:

tcontrol(min)=Ttx(min)+tcable+4Tscheduler(min)+tswitch

(1)

最小端到端延迟tend-to-end(min)也是确定的。如图1所示,tend-to-end(min)为以下几个变量之和:

tend-to-end(min)=tcontrol(min)+tfiber+tserial

(2)

tcontrol(min)、从交换机到接收器的光纤传输延迟tfiber,以及在接收器处波长分段数据包的串行化(反串行化)延迟tserial。

最小端到端延迟并不包括交换机处的任何数据包缓冲延迟,因为最小端到端延迟仅在无争用的情况下出现。tend-to-end(min)以tcontrol(min)为主;当控制平面处理请求时,数据路径中的相应数据包由网络接口处的分组控制器持有。当该保护时间过期时,分组控制器释放该数据包以进行传输,以便在其完成配置后立即到达交换机。

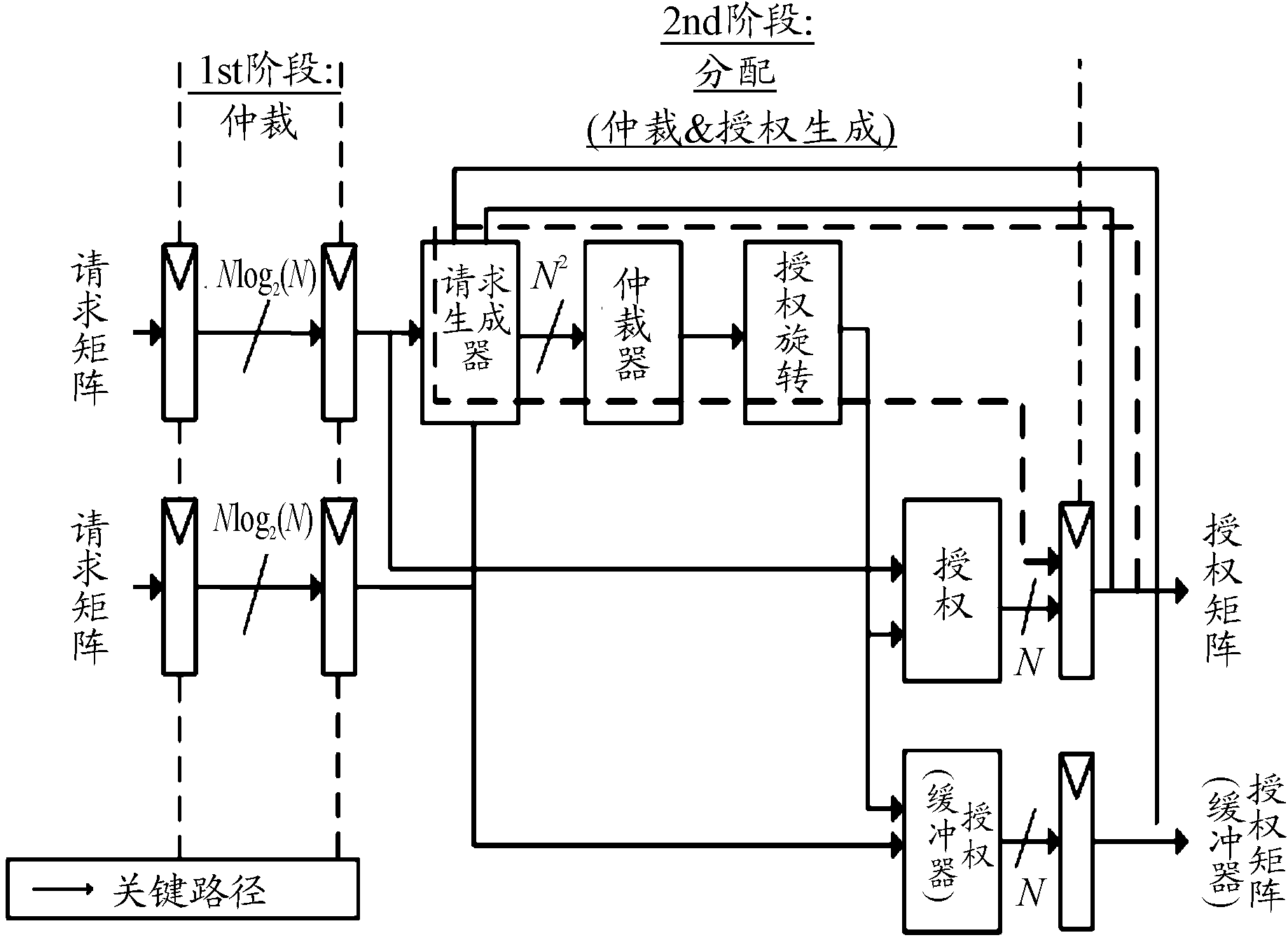

本文输出端口分配电路的简化框图如图2,基于轮转仲裁原则来执行分配。该电路有两个流水线阶段,即2个时钟周期分配(包括交换机配置)。在第一个流水线阶段,读取并寄存两个请求矩阵,一个用于新服务器请求,另一个用于交换机缓冲器请求。初始,请求按照输入端口排列,每个请求在log2(N)范围内,以寻址到目的地输出端口。因此,每个请求矩阵的大小为Nlog2(N)。第二个流水线阶段进行输出端口仲裁并生成新授权,即分配阶段。首先,请求生成器旋转每个请求矩阵以安排每个输出端口的请求,以便仲裁器能够读取请求,其后将两个矩阵复用为单个N × N矩阵R。在R矩阵中优先处理来自交换机缓冲器的请求,以保持包顺序并降低包延迟。并利用当前授权矩阵的反馈来移除任何已授权的请求。其后,对矩阵R进行分割并馈送到仲裁器,以建立新的N × N授权矩阵G。最后,对G进行反向旋转,以重新安排每个输入端口的授权,以待交换机配置控制器使用。

图2 单阶段输出端口分配电路框图

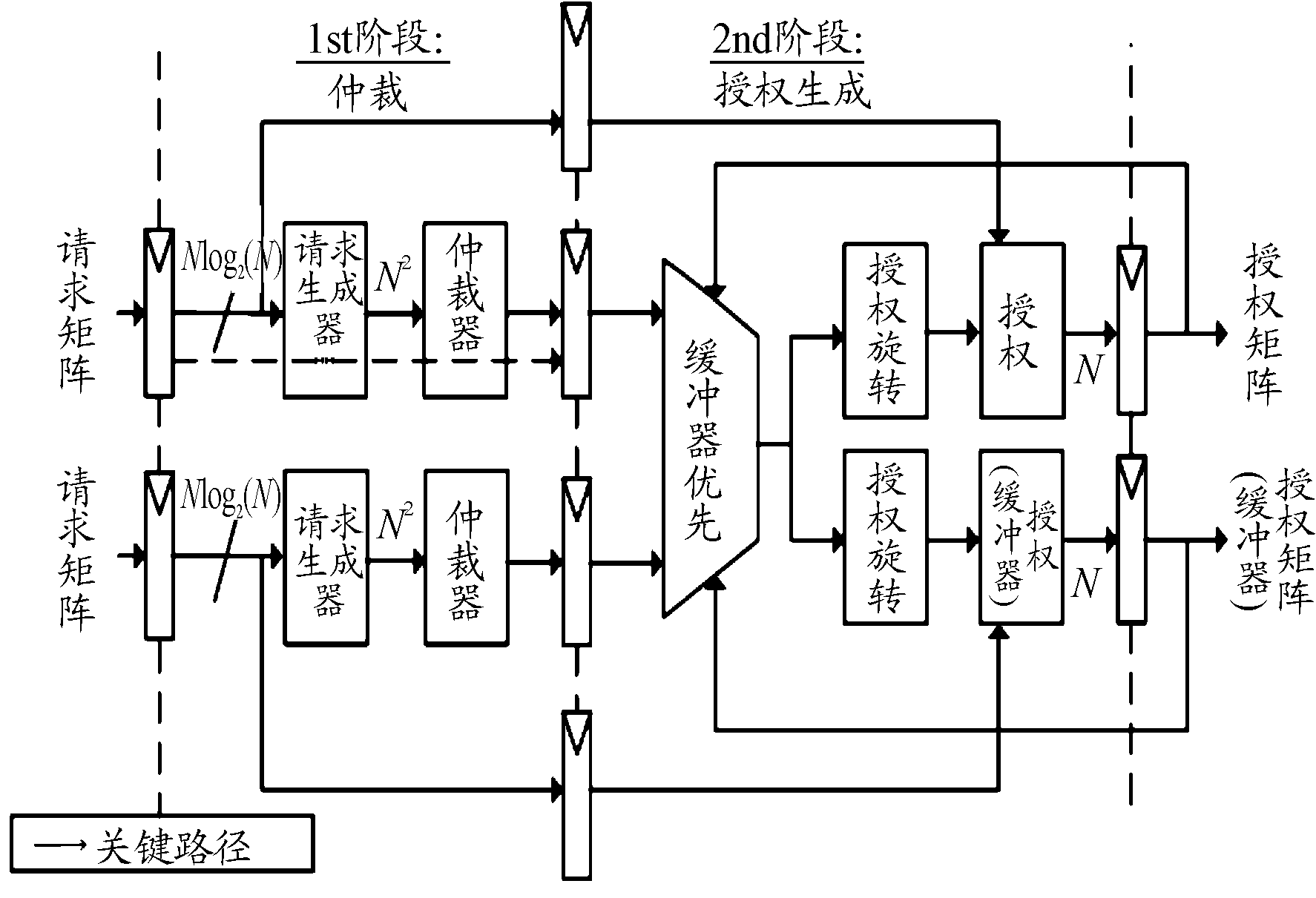

1.2 两阶段分配电路设计

最小分配电路时钟周期对于端到端延迟的下界至关重要。在本文使用的调度器中,虽然分配电路(图2)为两阶段流水线结构,但需要在单个流水线阶段中执行仲裁和新授权生成,由此产生一条很长的关键路径。为此,提出两阶段分配电路,如图3所示,分配电路设计通过以下方式缩短关键路径。

图3 两阶段输出端口分配电路框图

1) 仲裁和新授权生成分为两个流水线阶段。

2) 以并行的方式分别执行新的服务器请求和来自交换机缓冲器请求。因此避免了为仲裁器生成请求时的复用与优先级逻辑,优先级逻辑被移至第二个流水线阶段。

3) 将来自当前授权矩阵的反馈移至第二个流水线阶段,并应用于多路复用和新授权优先排序的逻辑。即:过滤掉新授权,而不用删除已经解析的请求。

由此,仲裁阶段的关键路径为:从输入请求寄存器通过仲裁器之一至仲裁器输出寄存器,如图3所示。首先,将两个输入请求矩阵Nlog2(N)均输入请求生成器逻辑中,以转换为仲裁器可读格式,请求矩阵扩展为N×N并进行旋转,以使得按照输出端口对请求完成分组。然后,将请求矩阵R和R′分别进行分割并馈送到N个N位的仲裁器。并行执行对R和的R′仲裁。寄存两个输出授权矩阵G和G′,并在下一个流水线阶段将其复用为单个 N×N矩阵,优先处理来自交换机缓冲器的请求。来自当前授权矩阵的反馈被用于滤除任何已发放过的授权。最后,使用并行逻辑模块对复用矩阵进行反向旋转,按照输入端口安排授权,然后为服务器请求和来自交换机缓冲器的请求生成N位授权向量。

2 实验与分析

2.1 控制平面实验

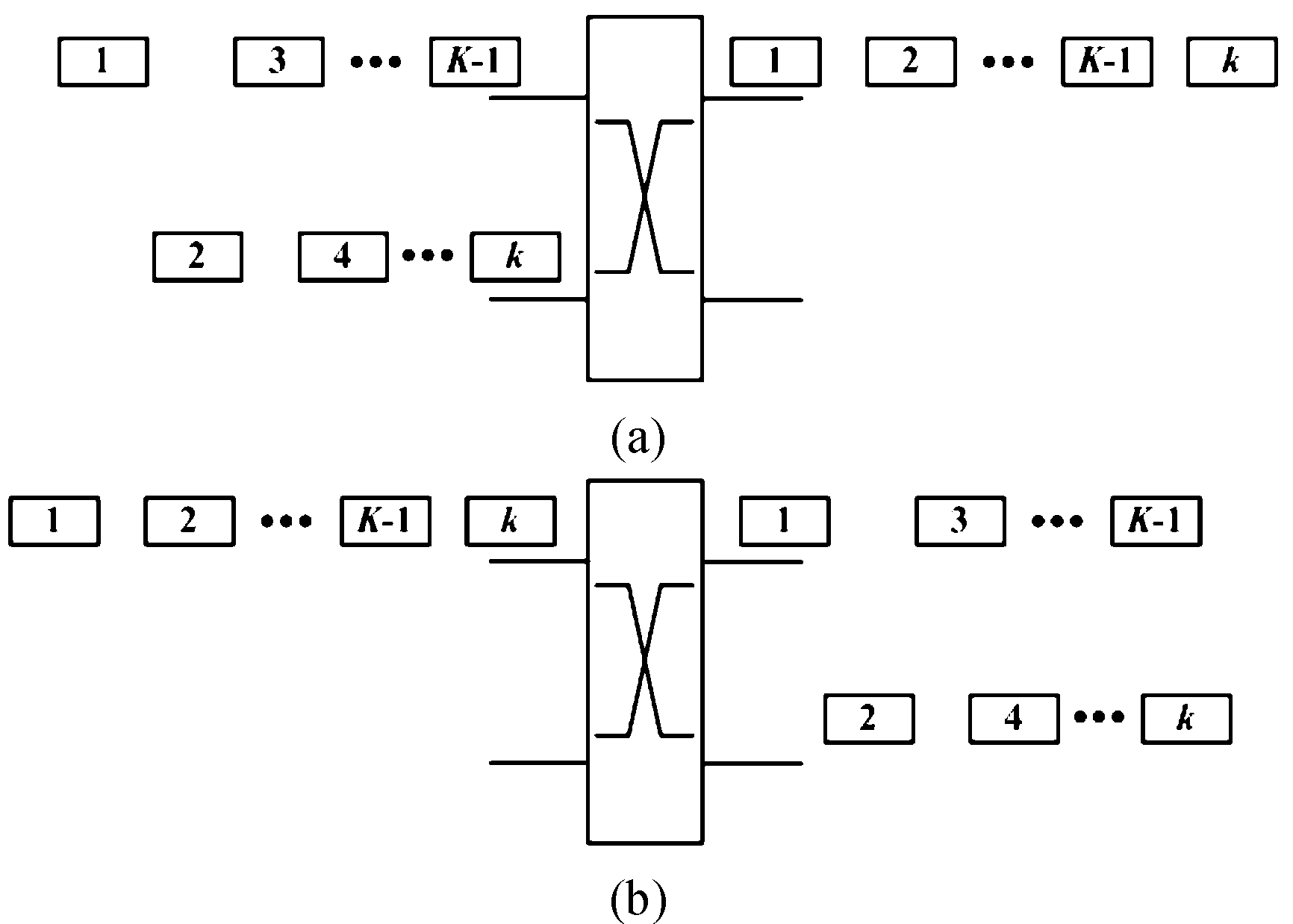

控制平面实验包括两个场景,如图4所示。图4(a)是从1个输入端口向2个输出端口进行分组交换;图4(b)是从2个输入端口向1个输出端口进行分组交换。

场景(a)

分组发生器每隔48 ns周期性地注入数据包,其目的地在两个可能的交换机输出端口之间交替。该实验旨在验证分组交换成功率,并测量最小端到端延迟。

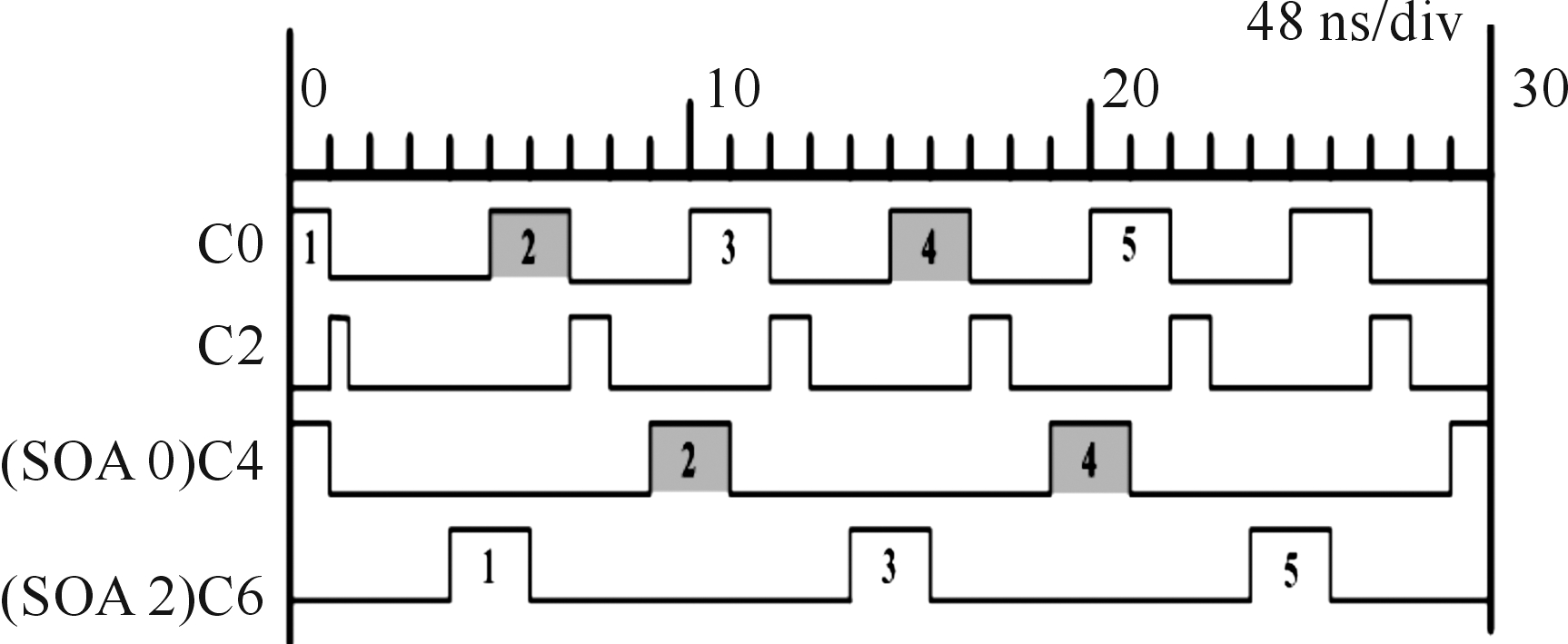

1) 控制路径信号。图5给出了利用ILA探针在调度器处捕捉到的控制进程的计时。首先输入请求(探针C0)被成功检测到(仅显示有效位)。其后,其在被分配电路(探针C2)检测到之前,先经历两个时钟周期的同步化阶段。最后,再耗费两个时钟周期来完成分配并为两个输出SOA(探针C4和C6)生成交换机配置信号。配置脉冲的宽度为两个时钟周期。如图5所示,每次只有一个输出SOA处于活动状态,由此将数据包交换至对应的输出端口。数据包在其他每个调度周期中均出现在同一个输出端口。

图4 两个实验场景示意图

图5 调度器处捕捉到的控制进程计时曲线

2) 数据路径信号。从服务器接口到两个输出端口的数据路径上不同点处的分组计时得出:数据包耗费36 ns离开FPGA,再需要12 ns以到达交换机SOA;其后,需要28 ns到达接收器;然后,接收器处的数据包反串行化耗费6.4 ns。由此得到的端到端延迟为82.4 ns,高于71.0 ns的期望值。

超出的延迟来自控制路径中额外的PCB轨迹和数据路径分立组件中的光纤尾纤,使得tcable和tfiber均超过了10 ns。SOA的放大效应使得每次打开SOA时均会出现电压偏移,该效应一般可通过光滤波器来移除。

场景(b)

该场景中,生成的所有数据包均被发送到相同的输出端口,但以恒定的时间差馈送到两个网络接口。通过数据包的交错到达,来分析不同网络接口的数据包之间的最小时间间隔,以测量交换机吞吐量。

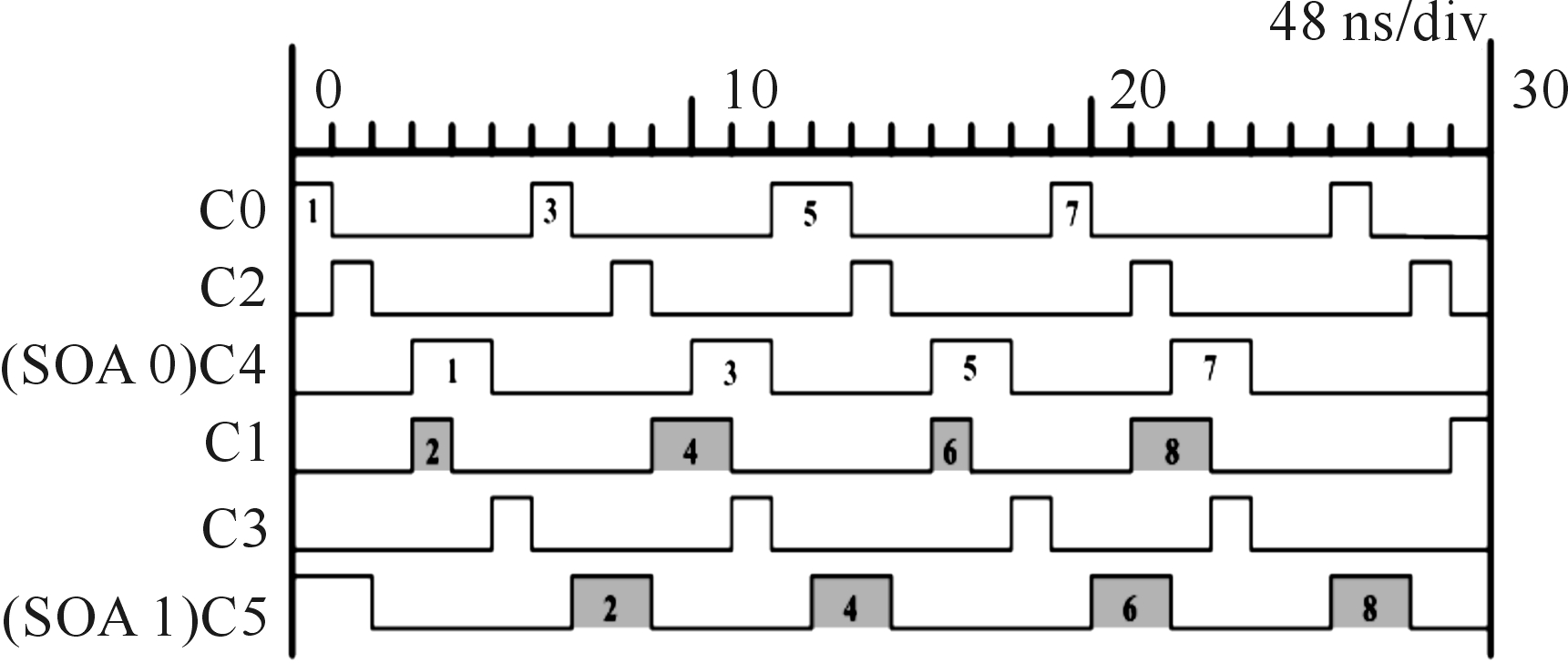

1) 控制路径信号。当调度器将交换机输出端口依次授权至两个网络接口时,其控制进程计时曲线如图6,可以看出,来自两个网络接口(探针C0和C1)的请求以固定时间差到达调度器。由于在每个网络接口处生成的请求的宽度为12.8 ns,一些请求可能会被寄存两次(取决于相对调度器时钟边沿的到达时间)。此处,调度器将输出端口(探针C4和C5)授权至最先请求的网络接口,然后在下一个调度轮中将端口授权至另一个接口。来自两个网络接口的请求之间的最小间隔为10Ttx(min)=32 ns。在运行在调度器时钟周期的ILA上,最小请求间隔为3Tscheduler(min)=28.8 ns。

图6 调度器对交换机授权的控制进程计时曲线

2) 数据路径信号。实验表明:来自不同网络接口的数据包之间的最小时间间隔为32 ns,主要源自控制平面的异步性。由此,吞吐量为(6.4/32)×100%=20%。利用同步的控制平面,来自不同源的数据包以Tscheduler为间隔,则最大吞吐量为(Tscheduler-tswitch)/Tscheduler×100=69%。

2.2 端到端延迟实验分析

本节基于SV语言[11]开发的网络模型,研究所提交换机系统的端到端延迟。分别分析了两种输出端口分配电路的延迟性能。对32×32的架顶光交换机进行了全尺寸机架规模的网络仿真,其中包括32个网络接口和32个交换机缓冲器。为避免100%负载下的丢包情况,每个缓冲器的深度设置为 2 014个分组。假定从机架到交换机的光纤长度为 2 m,从交换机到同一个机架或脊交换机的另一条光纤长度 2 m,波长分段数据包的tserial=6.4 ns,即,对于固定的比特率(例如400 Gb/s),波长数量可能会根据数据包大小而动态变化。该模型捕捉控制平面特性,并添加接收端的总光纤传输延迟和数据包反序列化延迟,以计算数据平面中的端到端延迟。

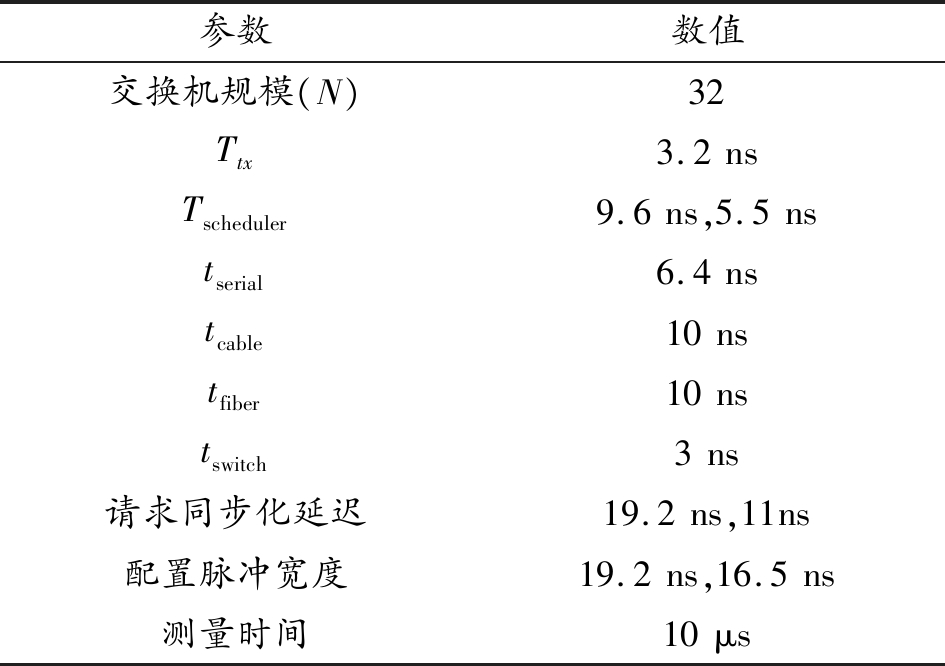

在综合工作负载下测量延迟性能。对一组(32个)独立的数据包源进行实例化,每个源基于到达间隔时间分布随机生成数据包。使用通用负载参数设置时钟周期中的数据包生成概率,从而控制源运行的容量百分比。其中,100%负载表示在每个时钟周期内,均生成数据包(没有时间间断)。数据包输出端口目的地是随机的,且每个包源馈送到一个专用的网络接口模块。网络仿真中使用的参数值如表1所示。

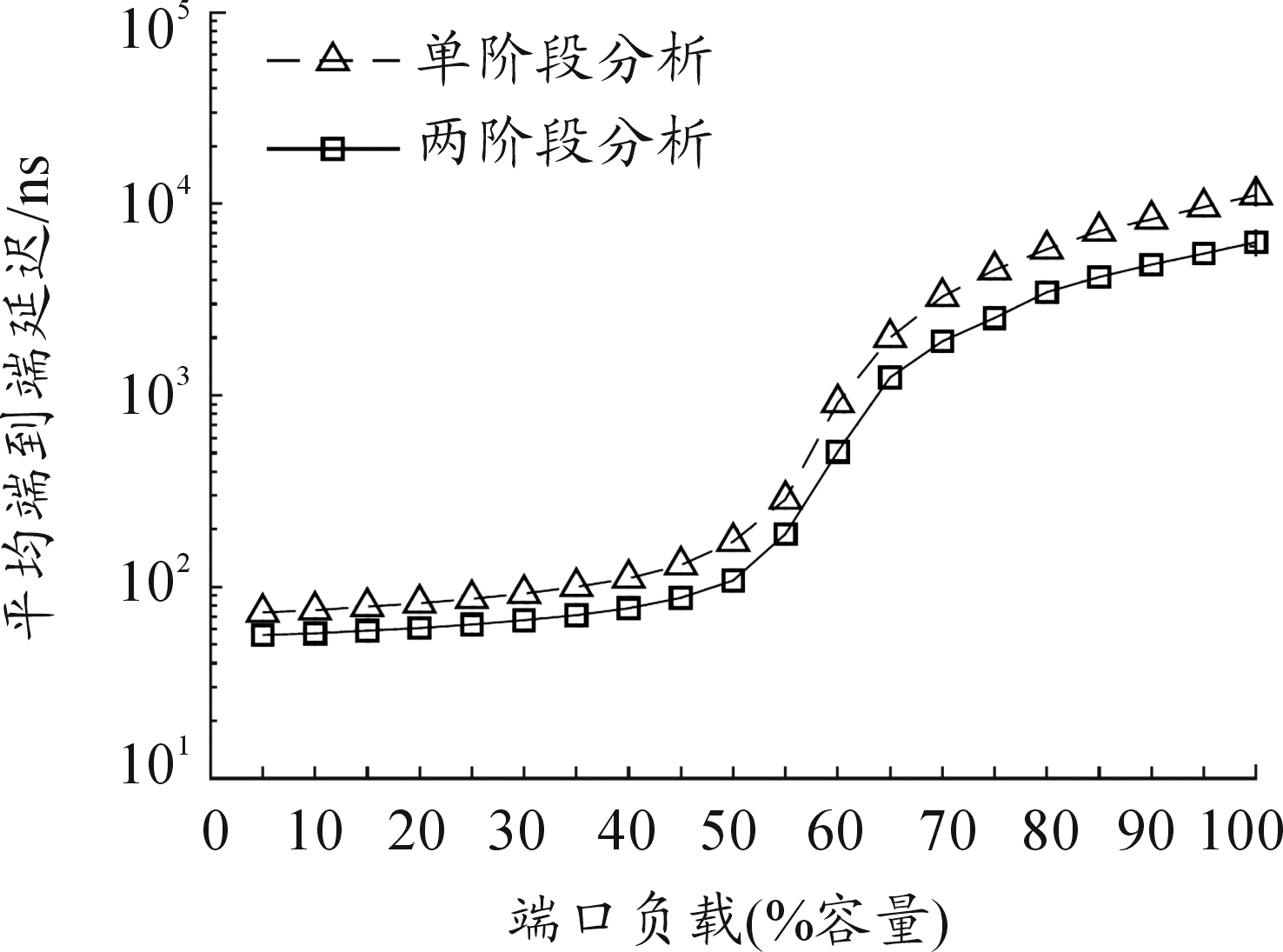

图7给出了对于单阶段和两阶段的两种分配电路,平均端到端延迟在不同负载下的变化情况。所有端口负载下,两阶段分配设计均取得较优性能。较低负载下,两种设计的曲线均收敛至期望的最小端到端延迟(式(2))。随着负载增加,争用概率上升,更多的数据包在交换机处缓冲,提高了平均端到端延迟。当负载超过50%时,由于大量数据包经历HOL阻塞,延迟迅速上升。在均匀随机流量下,两种分配电路在100%负载下的平均延迟均不超过10 μs。这些结果证明所提方法能够实现较低负载下的超低延迟交换。这主要得益于推测型传输,但会增加高负载下的缓冲。只要交换机缓冲器足够深(仿真中为 2 014个包),就可以避免丢包。另外,可通过改变交换机处的缓冲器放置来降低高负载下的平均延迟,在每个输入端口处根据每个输出端口实施一个虚拟队列,按照目的地顺序存放数据包,从而显著降低HOL阻塞,由此降低缓冲时间和平均延迟。

表1 网络模型参数介绍

参数数值交换机规模(N)32Ttx3.2nsTscheduler9.6ns,5.5nstserial6.4nstcable10nstfiber10nstswitch3ns请求同步化延迟19.2ns,11ns配置脉冲宽度19.2ns,16.5ns测量时间10μs

图7 端口负载容量与平均端到端延迟关系曲线

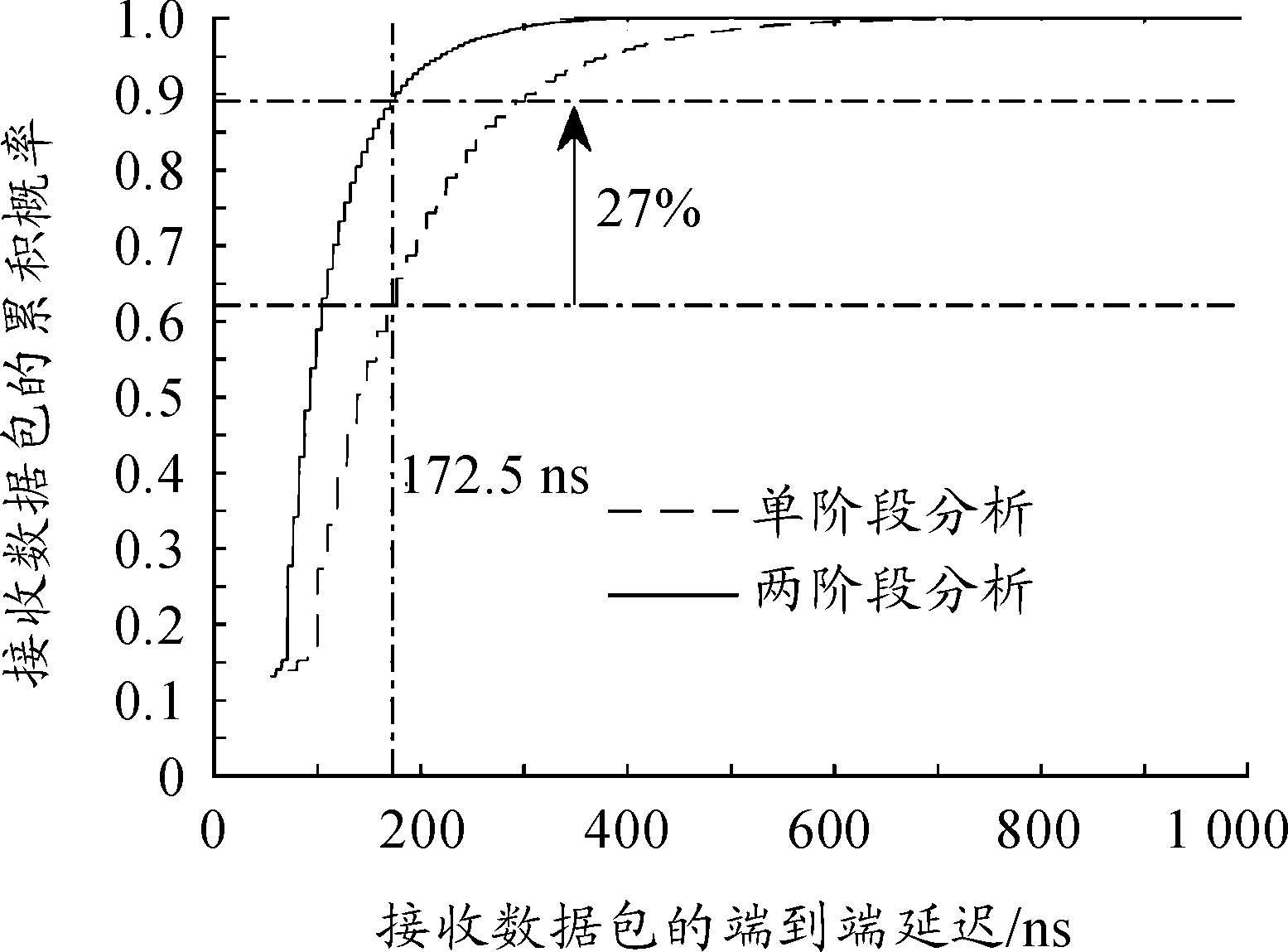

图8给出了50%负载下,两种分配电路的数据包端到端延迟的累积分布。在10 μs的窗口上,两种设计均以最小端到端延迟成功接收10%以上的数据包。单阶段分配电路的平均端到端延迟为172.5 ns。在该延迟数值下,两阶段分配电路提升了27%的分组交换量。此外,对于单阶段和两阶段分配电路,95%的数据包分别在71.2~377.5 ns范围和 55.2~219.6 ns的范围内接收,两阶段分配设计降低了158.6 ns的最长可能延迟。

图8 两种分配电路的数据包端到端延迟的累积分布曲线

3 结论

1) 提出了超低延迟控制平面的实施方法,并在32×32的纵横式光交换机上进行实验,在数据中心架顶应用中具有重要意义。

2) 提出了一个优化的电路设计,将分配分为两个阶段,缩短了关键路径,改善了调度器可扩展性。

3) 利用推测性传输并在交换机输入处存储数据包,降低了控制平面延迟,避免了在发送侧的授权同步化和处理操作。

[1] 王斌锋,苏金树,陈琳.云计算数据中心网络设计综述[J].计算机研究与发展,2016,53(9):2085-2106.

[2] 林初建,张四海.扁平化高校基础网络架构探索与研究[J].通信学报,2014(z1):107-112.

[3] LI X,LUNG C H,MAJUMDAR S.Green spine switch management for datacenter networks[J].Journal of Cloud Computing,2016,5(1):9-18.

[4] 陈博.基于物联网仿真平台的动态可配置网络系统的设计与实现[D].北京:北京邮电大学,2015.

[5] WANG G,ANDERSEN D G,KAMINSKY M,et al.c-Through:part-time optics in data centers[J].Acm Sigcomm Computer Communication Review,2010,40(4):327-338.

[6] 张春蕾,赵凯,杨勋发.基于RSOA再调制WDM-PON的移动前传调制方式[J].光通信技术,2018,42(2):9-12.

[7] 刘庆利,姚俊飞,刘治国.基于多业务的卫星光网络波长路由算法研究[J].系统仿真学报,2017,29(8):1780-1787.

[8] 何源.波分复用光网络支持云计算路由技术研究[D].南京:南京邮电大学,2017.

[9] 何璐蓓,厉俊男,杨翔瑞,等.RESSP:基于FPGA的可重构SDN交换结构[J].计算机科学,2018,45(1):205-210.

[10] ZHANG X,GUO L,HOU W,et al.Experimental demonstration of an intelligent control plane with proactive spectrum defragmentation in SD-EONs[J].Optics Express,2017,25(20):24837-24852.

[11] 黄凤英.基于SV语言的RFID标签芯片数字系统验证平台设计[J].中国集成电路,2016,25(3):30-34.