我国航天技术的飞速发展,数据存储一直在其中扮演着重要的角色。随着数字电子技术、计算机技术等相关科技的高速发展,大量、高速信息已经越来越出现在人们的日常生活当中,使得对数据的存储提出了更高的要求[1]。

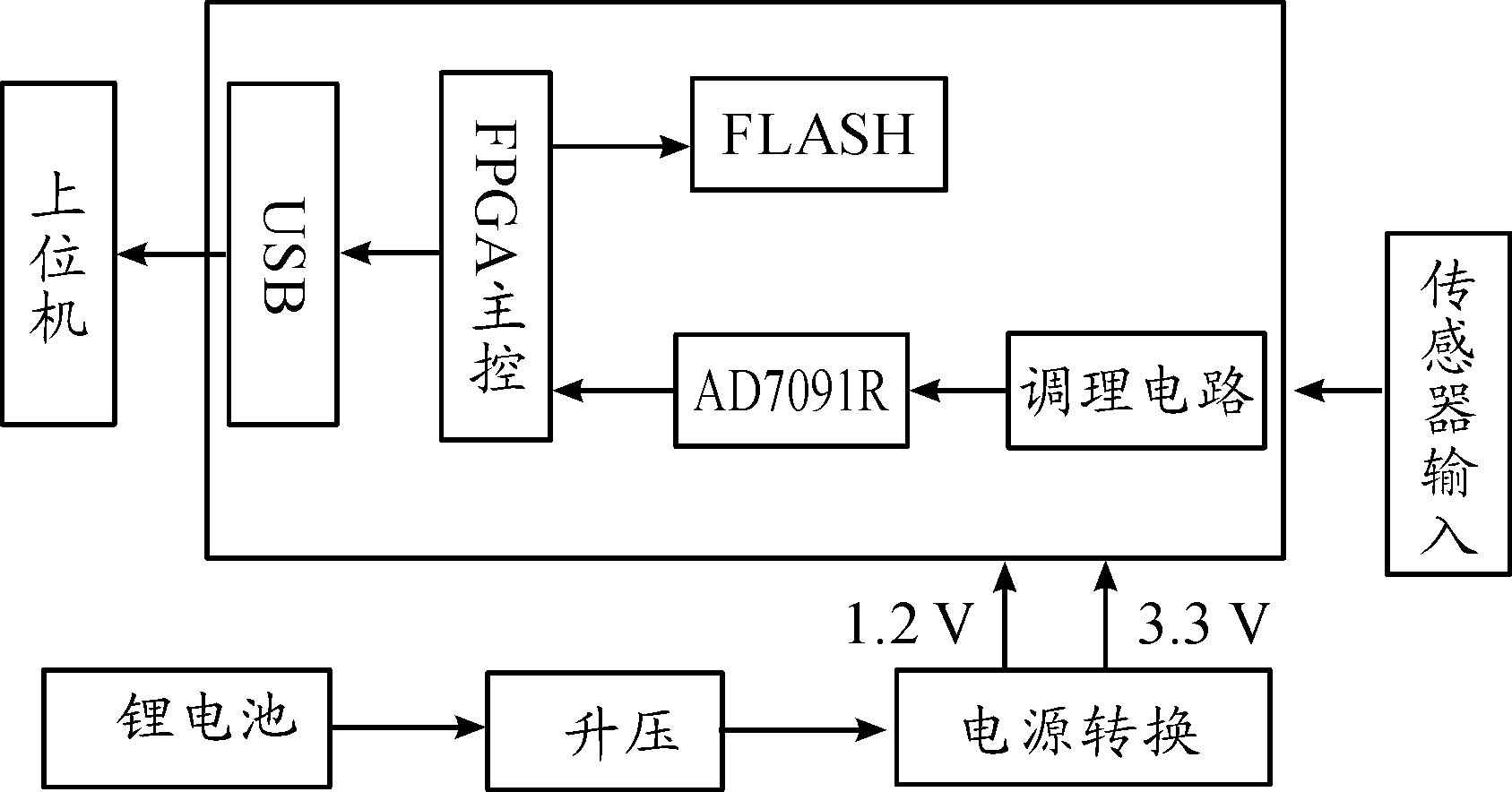

弹上传感器数据存储的准确性是影响其精度的主要因素之一。为了解决这一难题,本文设计的存储设备实现对传感器模拟信号的采集、处理,采用FPAG作为USB和FLASH的控制中心。模拟信号的采集采用AD7091R,通过FPGA存储至FLASH中,FLASH采用断电续存技术,使得传感器即使突然断电而不丢失数据,USB负责将存储的数据上传至上位机,实现对数据的分析和处理[2]。设备设计遵循小型化、标准化,并且能够承受外界冲击较大的载荷,同时实现数据高速存储[3]。设备通过锂电池供电,使得设备能够独立工作。

1 总体方案设计

设备主要实现即使面对突发情况,传感器数据仍能准确无误地存储到设备中。综合考虑各种因素,将设备做成圆柱体形状,底面圆半径为50 mm,高为60 mm。由于外形尺寸的原因,内部电路板必须小于外形,FPGA采用较小的BGA封装,AD7091R采用MSOP-10小型封装,升压芯片考虑到锂电池的供电以及封装等问题采用TPS63002。由于FPGA供电有1.2 V和3.3 V,而且整个设备所用的电源也是3.3 V居多,采用TPS70345电源转换芯片。

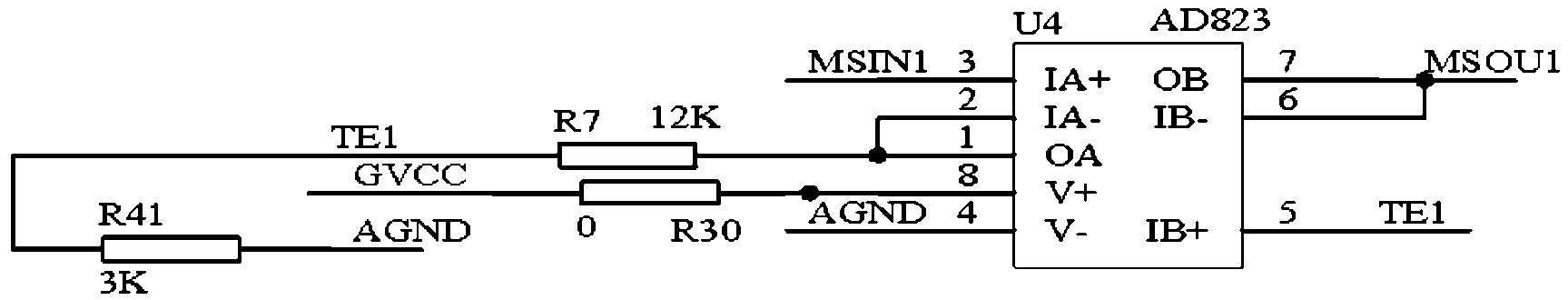

调理电路主要实现信号的跟随、分压、跟随,采用封装较小的AD823。每次上电设备采集2 h,而AD7901R每200 μs采集1次,2 h的数据量为411.987 M,FLASH采用4G的三星公司NAND型FLASH—K9WBG08U1M芯片[4]。设备总体设计原理如图1所示。

图1 设备总体设计原理框图

2 硬件电路设计设计

1) 供电电路设计

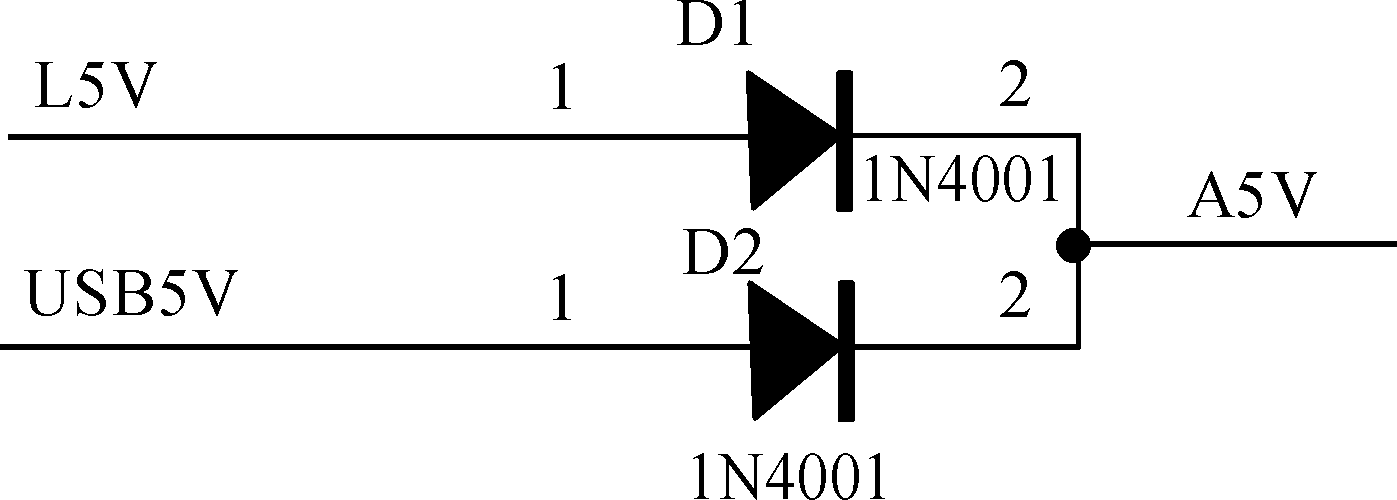

系统由供电锂电池和USB供电,双模式供电可以提高设备的可靠性,在数据传输的过程中不会因为锂电池出现问题而影响数据的准确性[5]。

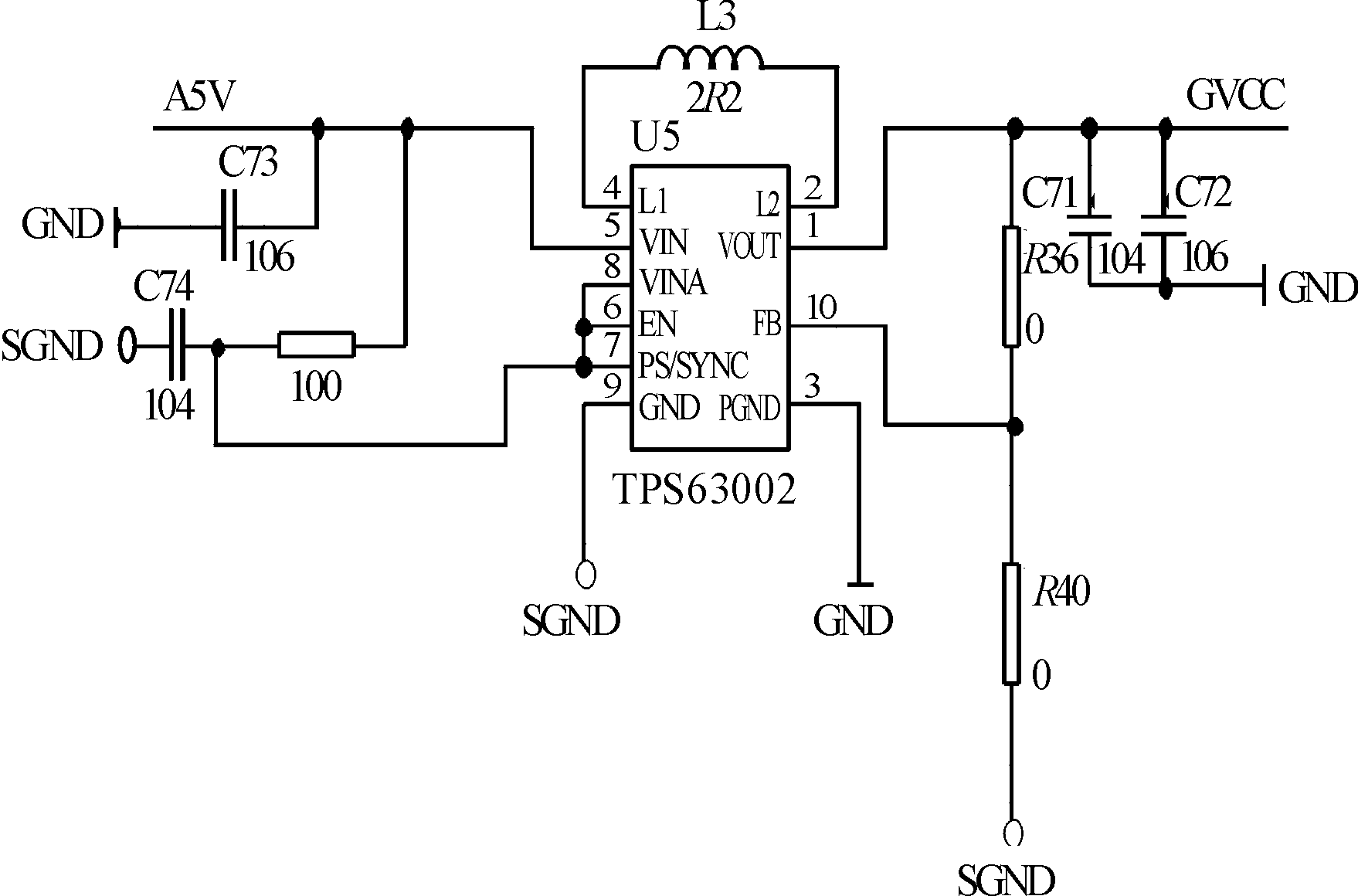

D1和D2用来控制L5V和USB5V其中一个供电,当一个二极管接通后,另外一个就相当于断开,同时也防止后续电压倒灌。如图2所示。电压通过二极管之后低于5 V,不能正常为电路板供电,因此再通过升压应芯片将电压升到5 V,具体如图3所示。随后5 V通过TPS70345芯片转换成3.3 V和1.2 V,为FPGA和其他电路提供电源。

图2 隔离电路图

图3 升压电路图

2) USB接口电路设计

USB不仅作为数据上传上位机的关键接口,同时也是为电路板供电的重要电源。考虑到数据量和实际要求,芯片选用FT232H[6],该串口的传输速度可以达到480 Mb/s。采用USB接口上传数据节省了电缆,并且更加便利,使整个设备的通用性增强。USB供电同时也节约了资源,其中C40和C41为USB5V过滤其他电压,使电路板的供电更加稳定。USB具体电路图如图4。

图4 USB硬件电路图

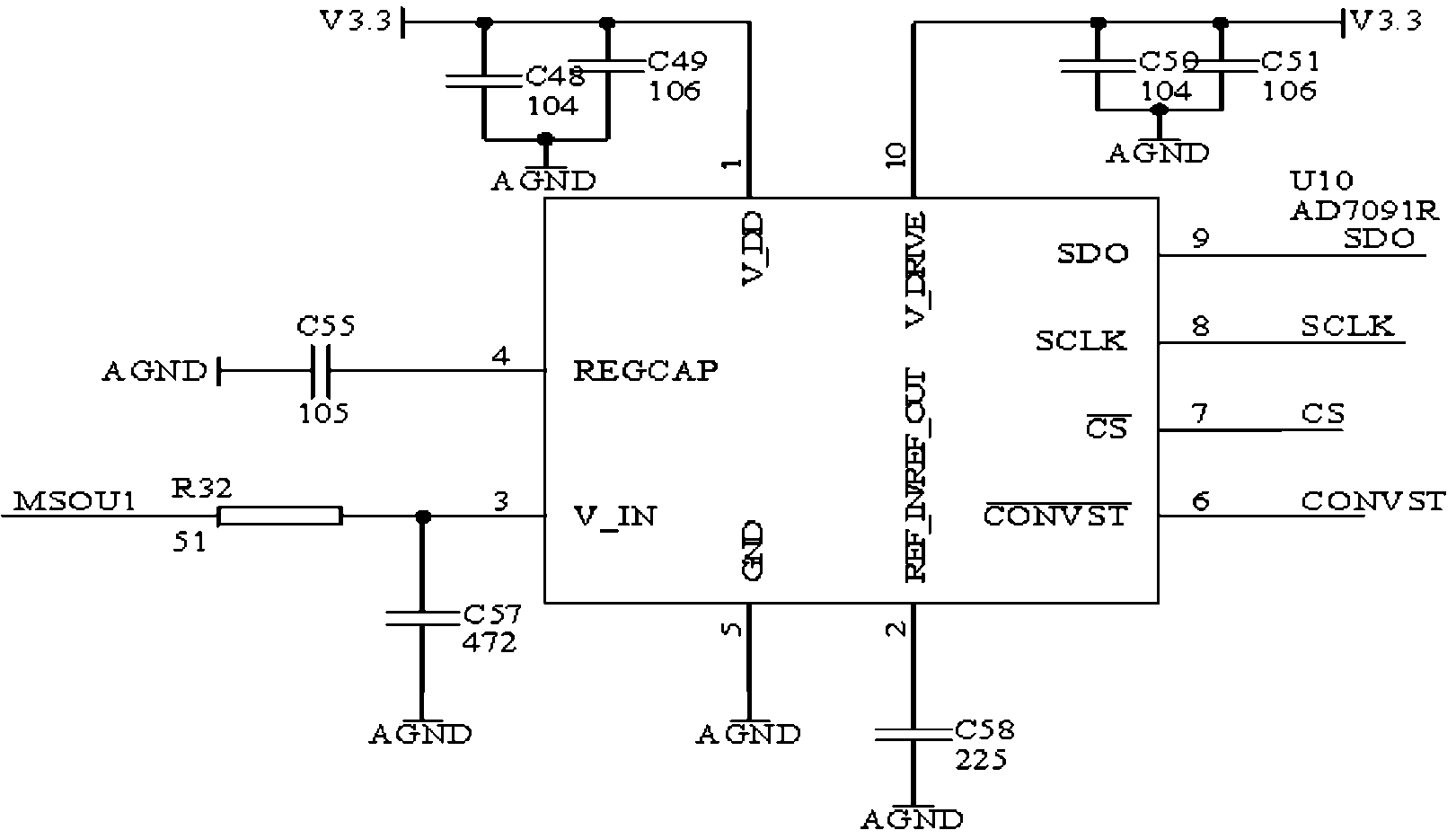

3) A/D采集调理电路设计

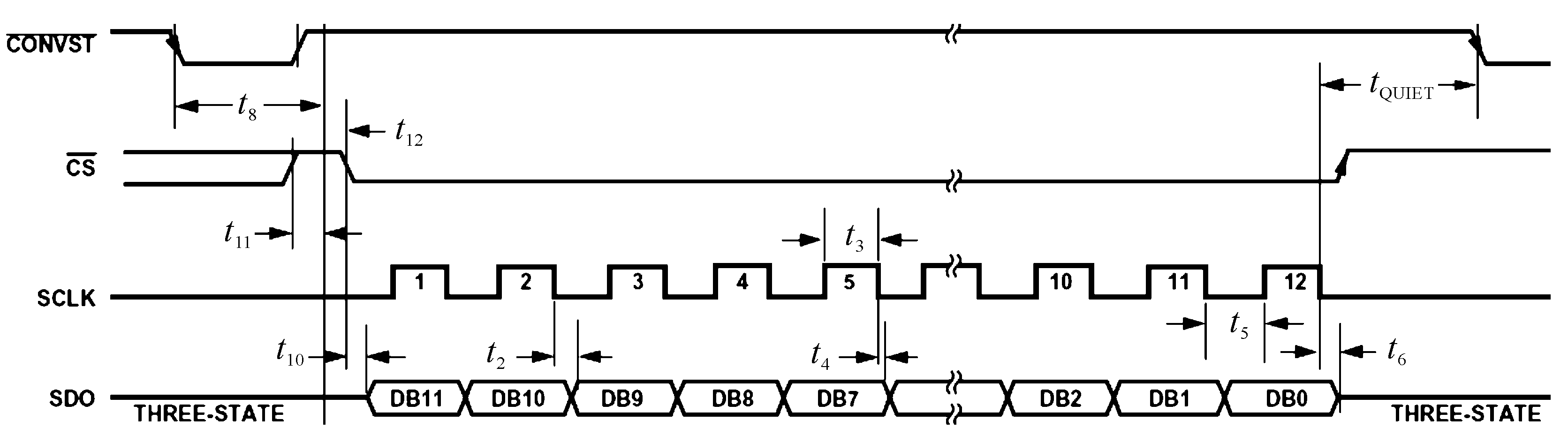

A/D使用1 Mbps、超低功耗、12位采样率的AD7091R,采集和转换过程主要利用CONVST控制,完成转换需要650 ns。使用外部基准电压源时,AD7091R从省电模式上电需要100 μs,A/D转换整个过程需要250 μs[7]。具体电路如图5所示。传感器模拟信号电压高于A/D转换芯片的工作电压,在进入A/D转换之前,需要调理。模拟信号的调理应用AD823实现电压的跟随、分压、跟随,使得信号更加准确。调理电路如图6所示。

3 关键技术

3.1 断电续存技术

断电续存技术是指在传感器存储设备上电后开始采集数据和存储数据过程中,如果遇到突发情况设备突然断电,重启后再次上电,设备可以从上次采集数据结束的地方再次进行数据存储,这样使得设备的可靠性更高,令设备可以在更加复杂的环境中使用。存储的过程中采用interleave two-plane page program的操作方式[8],使得存储速度可以匹配A/D采集的速率。

图5 AD7091R采集电路图

图6 调理电路图

根据FLASH制备的特质,每一个FLASH断电在断点出会出现一组FF块,只需存储过程中再次检测到这个FF块,之后以这个FF块为开始存储的地址继续存储数据就能够实现断电续存的功能,这样可以确保传感器数据的完整性。其中检测FF块流程如7所示。

先写入chip1的plane0的block0的第0页,接着再写入chip1的plane1的block1的第0页,当再一次回到chip1的plane0时,已经过了25 ns×4 096×7=716.8 μs,大于tPROG的最大值700 μs,所以不会影响到再一次操作chip1的plane0的block0。这种方式避免了编程时间tPROG对存储速度的影响,理论上可以达到40 MB/s的写入速度,足以满足A/D采集的速度。

3.2 A/D控制逻辑

设备上电由FPGA控制,FPGA根据传感器的工作情况进行供电。设备上电之后,首先启动AD7091R进行A/D转换。CONVST从高电平变成低电平后,开始启动A/D转换。数据在SCLK和CS的控制下输出器件。DB10到DB0是根据SCLK的下降沿输出数据,在完成最后一个数据输出之后,SDO返回高阻态。全部数据输出之后,SCLK为空闲低电平,确保数据准确性,整个过程需要650 ns。具体逻辑如图8所示。如果在进行转换时,再将CONVST拉低,重复上述周期。

图7 断电续存流程框图

4 测试结果

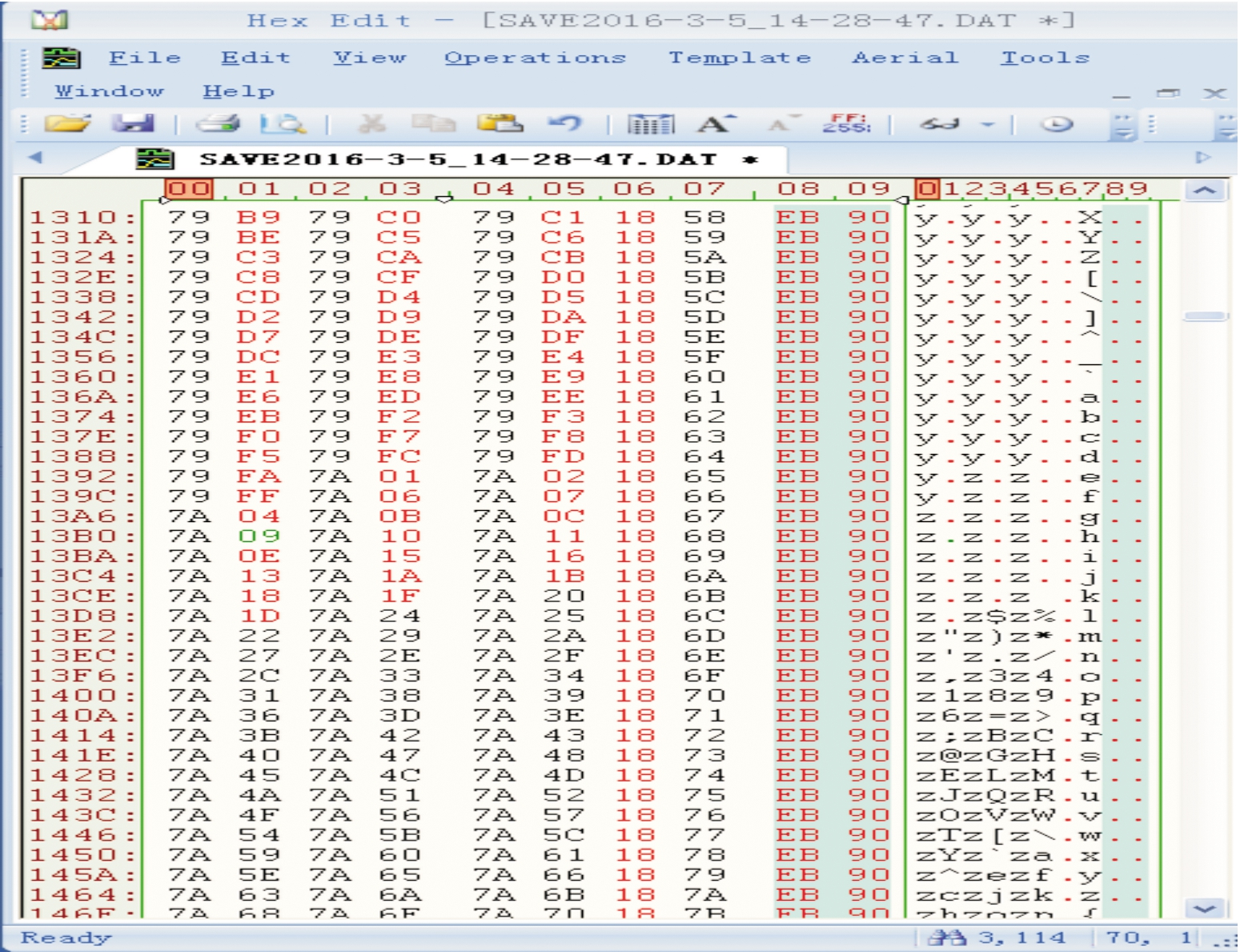

设备上电后,开始采集传感器信号,一段时间之后再断电。断电2 min之后再上电,分析采集回的数据,通过判断帧尾“EB90”和帧计数,确定数据准确无误,数据如图9所示。测试设备的存储速度达到30.72 MB/s,实现了数据的快速存储和实时存储。

图8 AD7091R逻辑示意图

图9 采集的数据页面

5 结论

设备实现了预期功能,解决了因断电导致设备采集数据不准确的问题,而且设备存储速度快,能够实时存储数据。同时,设备的整体尺寸特别小,使整个设备更加小型化、集成化。设备可以应用于采集时间长、存储速度快、数据量大的传感器采集系统上。

[1]王培人.数据采集器的FLASH存储技术与实现[D].哈尔滨:哈尔滨工程大学,2016.

[2]菅少坤.一种具有断电续存功能固态存储系统的设计[D].太原:中北大学,2015.

[3]郭鹏翔,祖静,尤文斌.基于FPGA与NAND闪存的固态存储系统设计[J].电子测试,2011(12):54-57.

[4]方彧,王杰.基于USB的高速多相机图像采集系统[J].信息与电脑(理论版),2017(10):98-99.

[5]任鑫,李泓锦.基于TMS320F2812的数据采集系统的设计[J].北华航天工业学院学报,2017,27(01):21-22.

[6]郑永秋.某飞行器遥测数据记录器的优化设计[D].太原:中北大学,2012.

[7]吴昊.高速大容量固态存储系统设计[D].西安:西安电子科技大学,2010.

[8]刘瑞.基于FLASH 的高速图像采集存储系统[D].北京:中国科学技术大学,2009.