高速飞散破片是杀爆战斗部中的重要毁伤元,其飞散速度是衡量战斗部威力效应的重要指标之一[1]。针对弹丸破片速度测试,当前以利用定距测时原理的接触式测量和非接触式测量为主[2]。非接触式测量法容易受到试验现场恶劣环境的影响,如战斗部爆炸时产生的瞬态高温、高压、强冲击等,降低测试系统对破片的探测和分辨能力,且使系统防护困难,导致测试误差较大,成本较高[3-5]。接触式测量法成本低,安装操作简单,满足一般靶场弹丸破片测速要求。但现有接触式测量法存在以下不足:铜丝靶网制作复杂,制作周期长;测试通道数固定,可扩展性较差;测试数据存储可靠性较差,上位机显示软件操作繁琐等。

针对上述接触式测量法存在的不足,本系统拟选用印刷电路板(PCB)工艺制作的梳状靶,以FPGA为控制核心,采用单片高速A/D转换器,通过多路模拟开关实现对32路断通靶信号的采集,然后将测试数据存储到非易失性NAND Flash中,并提出一种基于LabVIEW的上位机实现方案。

1 系统原理设计

梳状靶是一种典型的通靶,具有加工、使用方便、可批量生产等特点,通常为开路状态。当金属弹片打在梳状靶上时,梳状靶短路,由脉冲发生电路产生一个正的单脉冲信号[6-8]。根据定距测时法原理,在破片测速试验中,以战斗部爆心为原点,根据测试要求在距爆心距离为x1、x2、x3、…处面向爆心布设梳状靶,梳状靶的中心法线与爆心和梳状靶中心连线重合。各梳状靶通过信号线与测试系统各通道一一对应连接,同时在弹丸起爆位置布设线。弹丸起爆后,断靶线断开,测试系统接收到启动信号并开始记录,各通道获得统一的时间基准,系统对破片通过各梳状靶时产生的单脉冲信号进行存储,可以得到破片从弹丸起爆点到各个梳状靶布设点的时间,通过时间和距离可以计算出破片到达各测点的平均速度,通过破片到达不同距离梳状靶的速度可以推算出破片初始速度。梳状靶测速原理如图1所示。

图1 梳状靶测速原理示意图

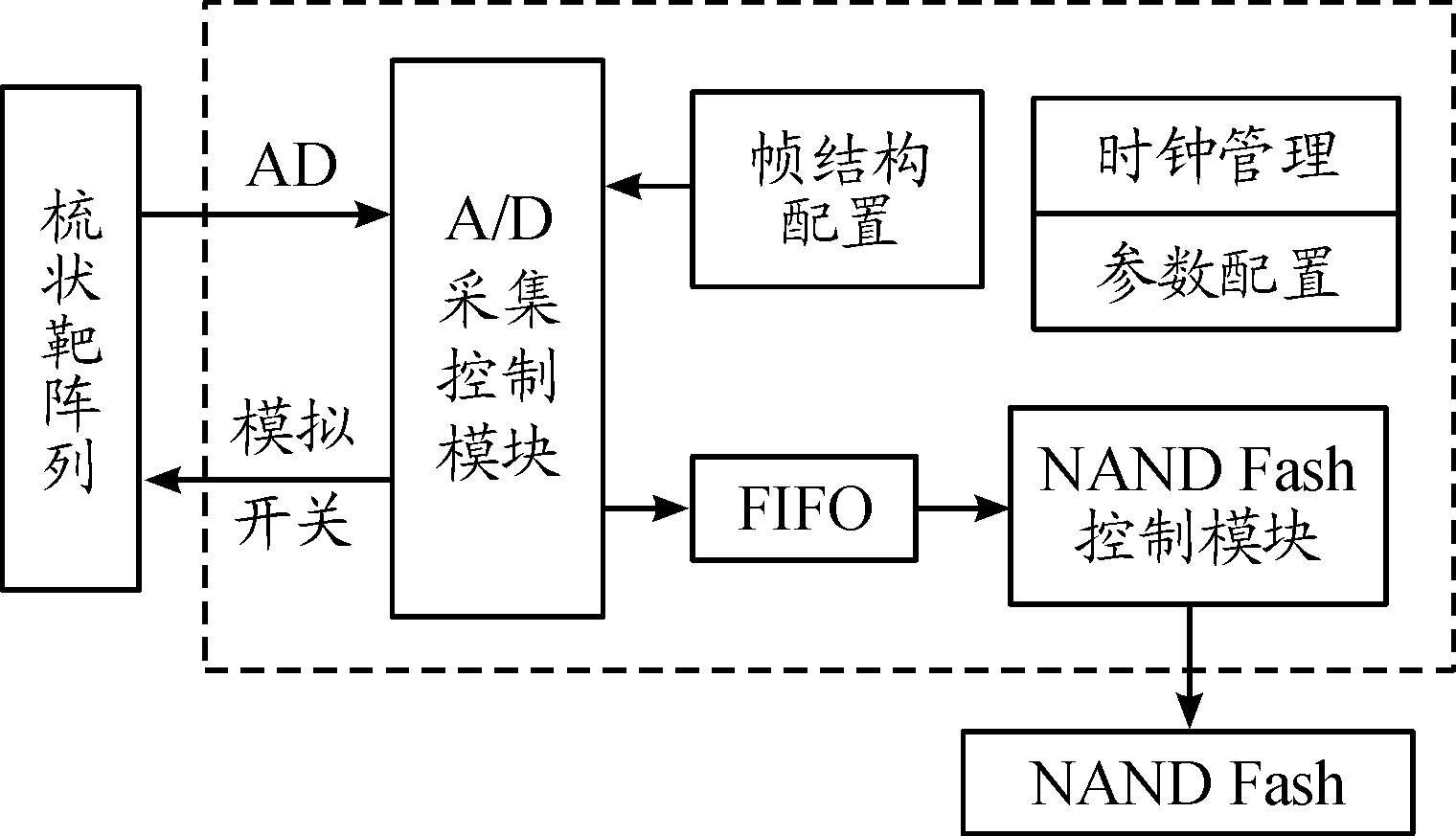

系统采用存储测试原理设计[9],主要工作是完成各路梳状靶产生的模拟脉冲信号的调理、采集、存储、传输和显示处理。由梳状靶(通靶)信号调理电路、A/D转换器、FPGA逻辑控制器、NAND Flash存储器、数据传输接口和电源管理模块组成。工作原理如图2所示。

图2 系统工作原理框图

系统工作过程:试验前,根据爆炸当量和各测点相对于爆心的距离对测试系统进行采样频率、存储长度等相关工作参数的设定;系统对设定好的工作参数具有记忆功能,此时系统可断电进入等待状态;然后在“起爆”信号之前,系统上电,进入循环采样阶段;战斗部起爆后,断靶信号使系统触发,各通道信号在同一时基下开始记录,将有效数据保存到存储器中;存储完成后可通过USB接口进行数据读取,利用上位机对测试数据进行显示处理。

2 关键技术

2.1 基于FPGA的采集控制逻辑设计

目前,现有存储式破片测速系统大多数采用多通道多A/D转换器的架构,控制器以单片机为主,且存储芯片多为SDRAM等易失性存储器,系统功耗较大、成本较高,且体积较大携带不方便[10-11]。本系统提出一种以FPGA为控制核心,基于单片高速ADC的采集逻辑控制方案。FPGA控制逻辑如图3所示。

图3 FPGA控制逻辑框图

2.1.1 多路模拟开关设计

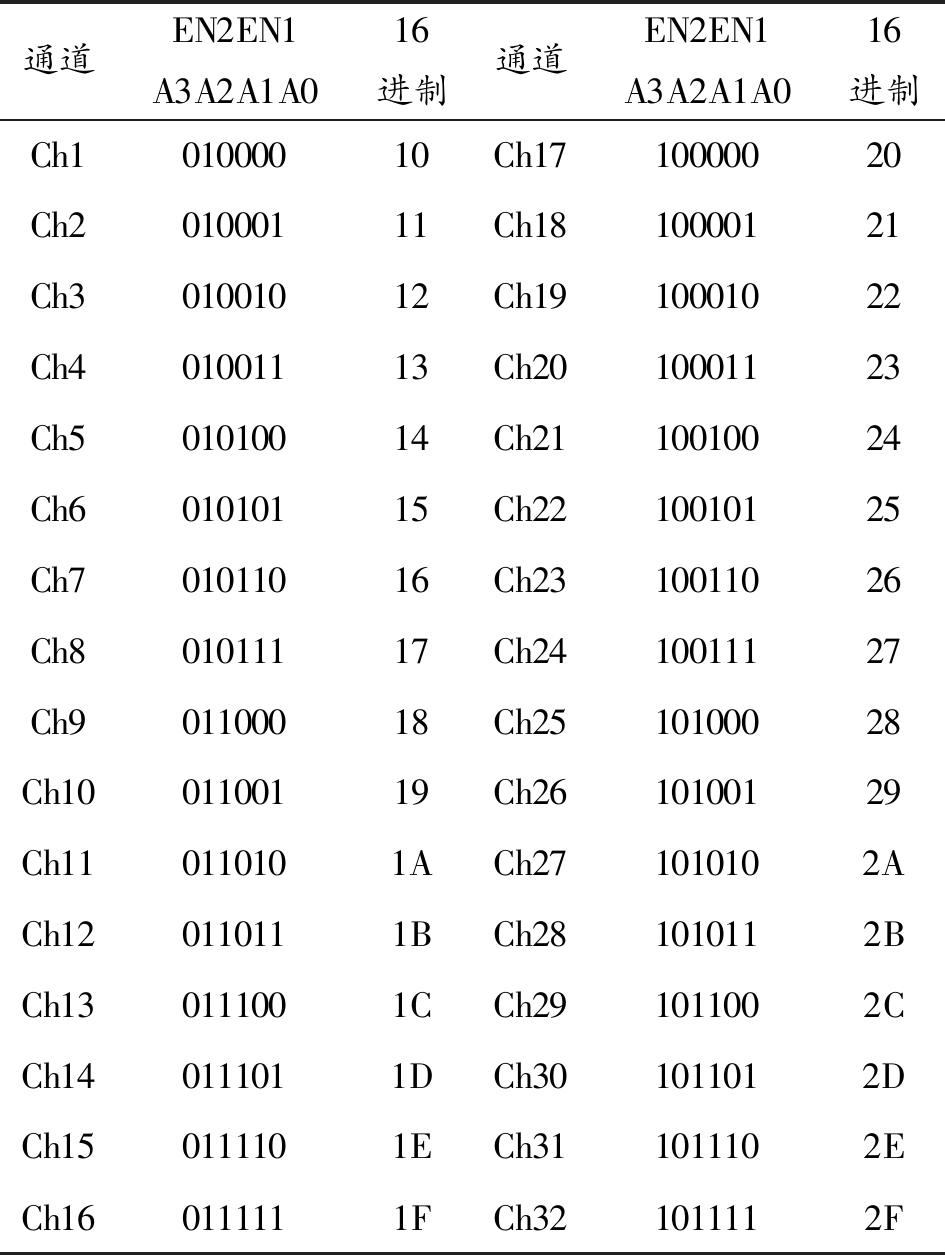

多路模拟开关的选取主要考虑以下指标:通道数量、导通电阻、泄漏电流、切换速度和芯片电源电压范围等[12]。系统选用ADI公司的16选1高速模拟开关ADG706,其导通电阻为2.5 Ω,电阻平坦度为0.5 Ω,泄漏电流为100 pA,切换速度高达16 MHz,-3 dB带宽为25 MHz,电源电压范围为1.8~5.5 V,满足设计要求。FPGA逻辑电平的上升和下降时间都很短,可实现时序逻辑的精准控制[13],两片ADG706可在FPGA控制下采用级联的方式实现32路通道切换。两片ADG706芯片的模拟选通端A3~A0以及使能端EN与FPGA相连,通过控制EN1、EN2实现两片ADG706的选通,然后通过控制被选通ADG706的A3~A0实现该芯片上16路通道的选通。各通道与控制代码间的对应关系如表1所示。上述设计让系统只需使用单片ADC,减少了器件数量,简化了电路设计,使系统体积减小,成本和功耗降低。通道选通控制仿真波形如图4所示。

表1 通道选通信号

通道EN2EN1A3A2A1A016进制通道EN2EN1A3A2A1A016进制Ch101000010Ch1710000020Ch201000111Ch1810000121Ch301001012Ch1910001022Ch401001113Ch2010001123Ch501010014Ch2110010024Ch601010115Ch2210010125Ch701011016Ch2310011026Ch801011117Ch2410011127Ch901100018Ch2510100028Ch1001100119Ch2610100129Ch110110101ACh271010102ACh120110111BCh281010112BCh130111001CCh291011002CCh140111011DCh301011012DCh150111101ECh311011102ECh160111111FCh321011112F

图4 通道选通控制仿真波形

2.1.2 多通道数据编帧

根据对梳状靶产生的脉冲信号的采样需求,要求各通道采样率达到1 MHz,所以32路总采样率为1 MHz×32=32 MHz。为方便时序逻辑设计和信号采样率控制,将采样的数据帧设置为固定格式,数据帧结构格式如表2所示,以行为单位进行各通道模拟信号的A/D采集。因各通道采样率均需满足1 MHz,故每个采样点采样频率取1 MHz。在帧尾增加帧计数FH、FL和帧结束标志55、AA,便于上位机回读数据时检测是否发生丢帧和误帧。因此一个完整的帧结构为6×6的矩阵,一帧数据的总采样率为1 MHz×6×6=36 MHz,总数据量为2 byte×36=72 byte。该帧结构保证各采样点均匀采样,使多路数据有序写入存储器,且在上位机读取数据后便于区分各路模拟信号的量化数据。

表2 数据帧结构格式

序号1234561Ch1Ch2Ch3Ch4Ch5Ch62Ch7Ch8Ch9Ch10Ch11Ch123Ch13Ch14Ch15Ch16Ch17Ch184Ch19Ch20Ch21Ch22Ch23Ch245Ch25Ch26Ch27Ch28Ch29Ch306Ch31Ch32FHFL55AA

帧结构设计完成后,利用FPGA中丰富的IP核资源例化一个ROM IP核,用于帧结构的配置。将表1中16进制的通道选通信号按表2所示数据帧结构格式写入ROM中的帧结构配置文件,实现多通道的地址切换,保证了各通道在规定的采样率下进行采样。通过调整帧结构可以对选通的通道数进行灵活选择,也可以根据需要改变特定通道的采样率。

2.1.3 A/D采集控制逻辑设计

由每帧数据总采样率为36 MHz,且采样周期需远大于ADG706的切换时间,系统选用ADI公司16位、采用多级差分流水线架构的模数转换器AD9266-40,芯片内部模拟电路1.8 V供电,数字电路3.3 V供电,最高采样率可达40 MHz,工作时钟CLK+、CLK-和模拟信号输入VIN+、VIN-均采用差分输入,可提高信号精度,抑制共模干扰。AD9266-40与FPGA间的接口连接如图5所示。

图5 AD9266-40与FPGA接口设计框图

工作时钟AD_CLK+、AD_CLK-电平标准为LVPECL,供电电源2.5 V,由FPGA的Bank3直接提供,且时钟频率为36 MHz。数据输出格式可由AD_SCLK/DFS配置,在SPI模式禁用时,DFS为高电平时,输出数据为二进制补码,DFS为低电平时,数据输出为二进制偏移码。输出数据数字时钟AD_DCO为36 MHz,每次采样值分两次输出,在AD_DCO上升沿输出采样值的8位偶数位,下降沿输出8位奇数位,且在FPGA中完成拼接。系统总体采集控制流程如图6所示。

图6 采集控制逻辑流程框图

2.2 基于LabVIEW的上位机软件设计

本系统实现了一种基于LabVIEW的上位机设计方案。LabVIEW是基于数据流的编译型图形编程环境[14],可灵活选择特定通道数据在同一窗口显示,且为各通道测试曲线分配不同的颜色,利用游标对所选通道之间的时间间隔实时显示。与Visual Basic相比较,利用LabVIEW开发的应用程序具有更容易扩展、便于维护的特点。

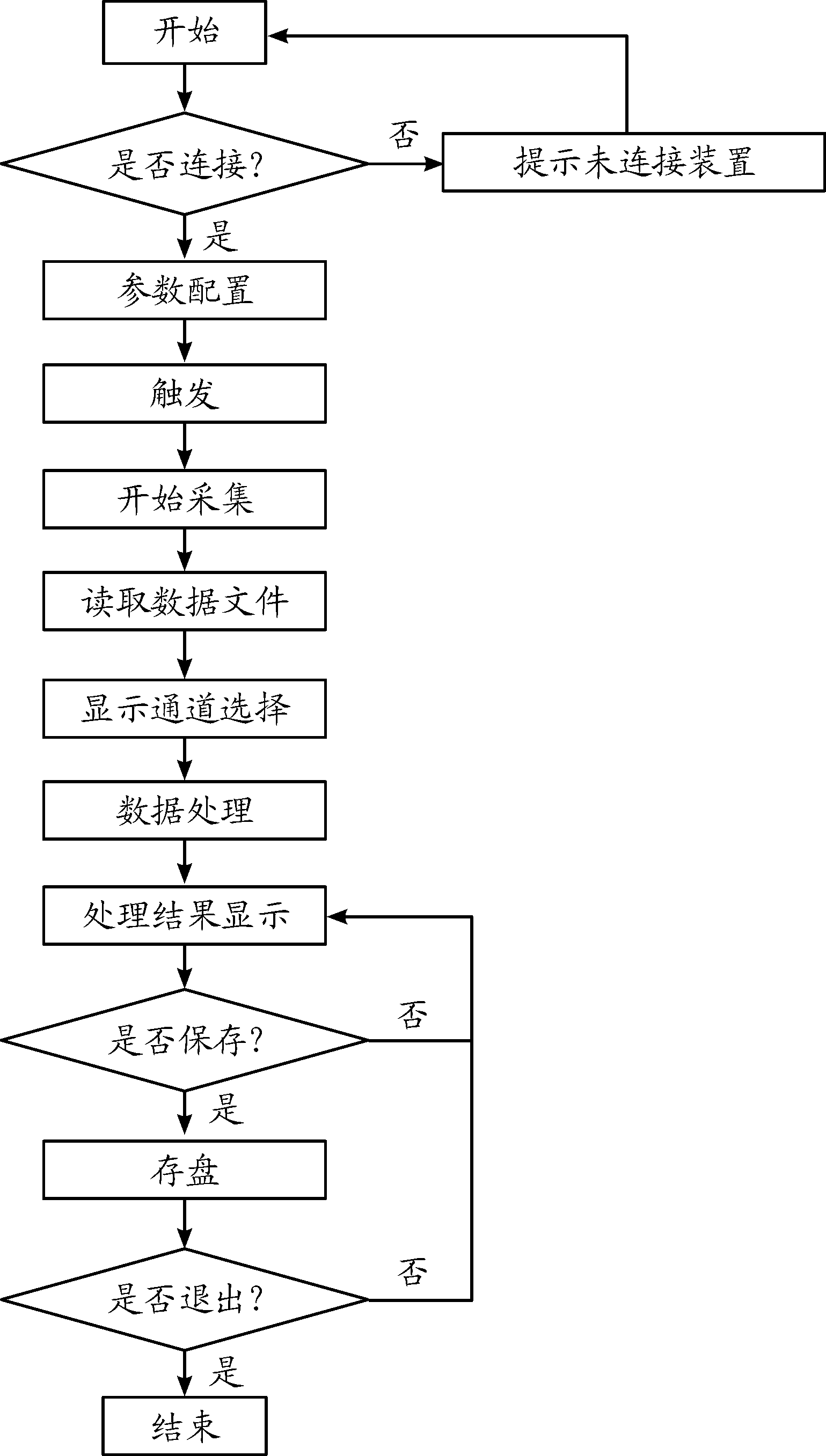

上位机主要包括以下功能模块:启动界面、通信模块、配置模块、自动标定模块、文件存储和转化模块、实时预览、回放功能、多功能信号分析和系统操作功能等。上位机操作流程如图7所示。

图7 上位机操作流程框图

3 试验验证

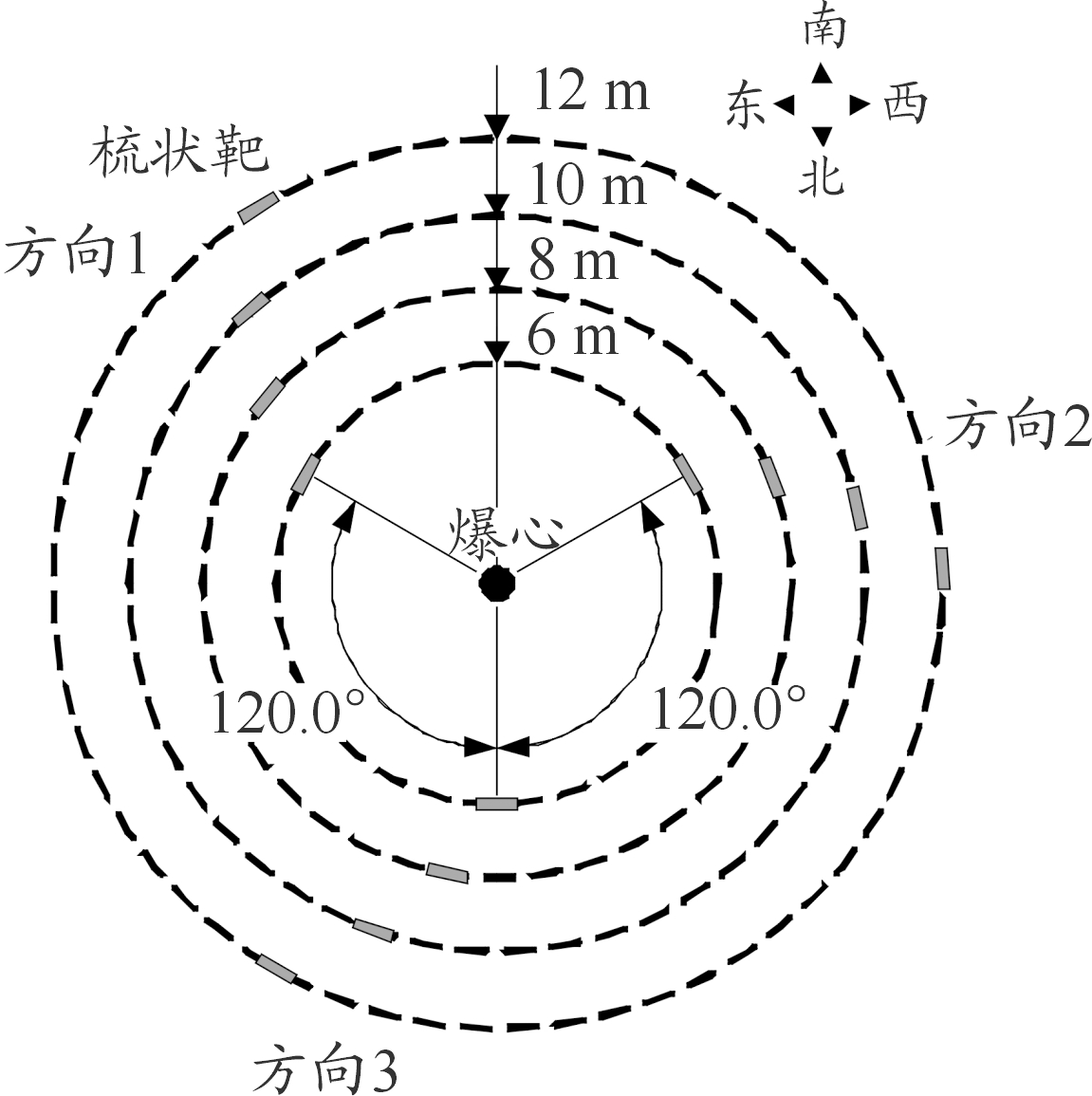

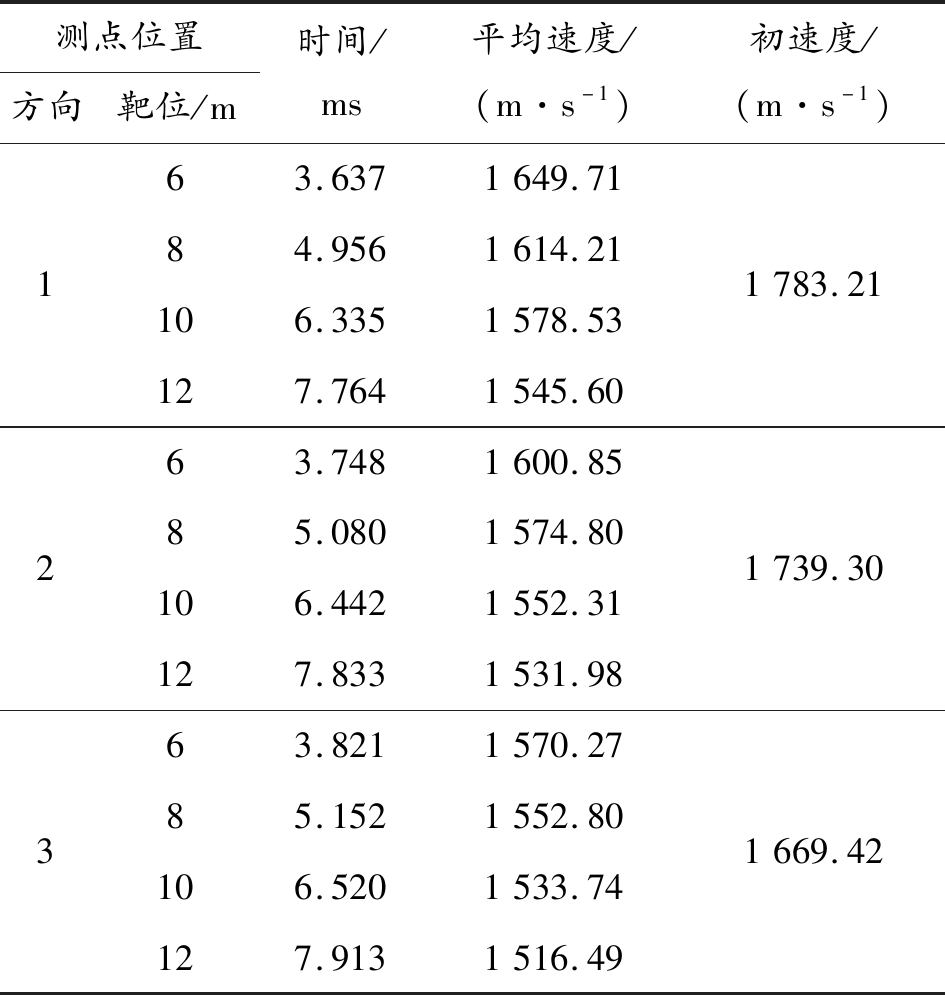

本系统已在多次实弹靶场弹丸破片测速现场试验中得到成功应用,充分验证了其准确性、通用性及可靠性。图8是某型弹靶场破片测速试验现场布局,将被测弹用木质支架架设到离地面1.5 m高度处,爆心取为被测弹中轴线到地面的投影。梳状靶布设在地面上以爆心为圆心夹角约为120°的3个方向上,每个方向布设4个梳状靶,且同一方向的4个梳状靶交错布设并由金属支架架高1.5 m,各靶到爆心的距离分别为6 m、8 m、10 m和12 m。测速系统由一路断靶信号触发启动记录,各测点具备统一时基。图9是数据处理阶段上位机的显示波形图,表3是一次试验后3个方向的数据测试结果。从测试结果可以看出,破片速度随着测点距离的增加是单调递减的,符合一定的衰减规律[15]。

图8 某型弹弹丸破片测速现场布局示意图

图9 上位机显示波形图

表3 某型弹一发测试结果

测点位置方向靶位/m时间/ms平均速度/(m·s-1)初速度/(m·s-1)163.6371649.7184.9561614.21106.3351578.53127.7641545.601783.21263.7481600.8585.0801574.80106.4421552.31127.8331531.981739.30363.8211570.2785.1521552.80106.5201533.74127.9131516.491669.42

由多次试验后的上位机显示波形与测试结果可以看出,采用本系统测量的数据捕获率较现有测试系统更高,数据准确率高,同时本系统在现场使用时操作简单,大大提高了测试效率。

4 结论

1) 经多次现场验证,本系统捕捉有效梳状靶断靶信号的通道数在95%以上,为各类弹丸破片杀伤力评估提供了有效可靠的测试手段。

2) 测试人员可根据具体测试任务进行通道数的灵活选择和系统工作参数的可编程设置,同时上位机软件操作直观简单,数据处理准确高效,满足对不同弹丸破片的测试需求。

3) 与现有接触式破片测速系统相比,本系统具有通道可灵活配置与扩展、可靠性高,上位机操作智能化、交互性好,测试数据精确度高等优点。

[1] 黄正祥,高森烈,李良威,等.小口径弹丸破片的测速方法研究[J].南京理工大学学报,2000(5):466-468.

[2] 李丽萍,孔德仁,易春林,等.战斗部破片速度测量方法综述[J].测控技术,2014,33(11):5-7,13.

[3] 许地鑫.靶网测试法在破片初速测试中的应用[J].现代测量与实验室管理,2012,20(1):13-15,18.

[4] 刘吉,赵冬娥,于丽霞,等.激光光幕战斗部破片速度测试系统的信号处理[J].弹箭与制导学报,2013,33(2):49-51.

[5] 李良威,娄国伟.高速摄影法测量弹丸的破片速度[J].高速摄影与光子学,1991(4):438-442.

[6] 杨桂红,王广军,龚晏青,等.梳状靶法研究爆轰驱动全预制破片的飞行规律[J].含能材料,2013,21(5):656-659.

[7] 刘瀚,任杰,王伟,徐豫新.印刷电路(PCB)靶在破片速度测试中的应用[J].测试技术学报,2018(1):26-30.

[8] 纪留利.断靶调理电路的设计与分析[J].黑龙江科技信息,2011(29):81.

[9] 马铁华,祖静.冲击波超压存储测试技术研究[J].仪器仪表学报,2004(S1):134-135,146.

[10] 车大建.基于VXI总线虚拟仪器技术的破片测速系统研制与应用[D].长沙:国防科学技术大学,2004.

[11] 李佳潞,赵冬娥,刘吉.基于最小均方算法的破片测速信号处理方法[J].探测与控制学报,2015,37(4):97-100.

[12] 陶海军,张一鸣,曾志辉.基于AD7606的多通道数据采集系统设计[J].工矿自动化,2013,39(12):110-113.

[13] 张传民.某弹载多通道数据采集系统的研究与设计[D].太原:中北大学,2015.

[14] 黄志强.基于LabVIEW多通道数据采集系统设计与调试[J].机械制造与自动化,2019,48(1):179-181.

[15] 马永忠,李其祥,杨光.对弹丸破片速度衰减规律的探讨[J].弹箭与制导学报,2000(3):59-64.