在航空航天及各类工业作业中,各类信息常需通过串口进行现场传输存储以便后续准确分析[1]。但随着各类控制系统规模的不断增大,串口采集的信息种类也越来越多[2]。对大容量多通道串口数据的采集存储方案也提出了关键数据的优先定位和读取、小体积、低误码率及环境适应等要求。

近年来NAND Flash以其非易失性、高可靠性、宽温度范围成为大容量存储介质的首选[3]。通常在Flash作为多通道系统存储单元的场合中,多通道数据需按照一定的帧格式顺序写入Flash,离线分析时也按此帧格式进行通道区分和处理[4]。这种方法需遍历存储器的所有地址数据,在取出数据后再进行二次区分处理。而实际经验表明:各类信息的数据输出并非持续整个采集时段,甚至关键数据只是全部数据的某一段或几段;当只有少量通道工作时,帧格式存储的方案在读取时仍需遍历全部地址和数据,造成存储资源的不均衡使用且降低工作效率;当多通道同时工作时,若因某通道故障或者数据包流速不规则,帧结构存储方法易造成数据的覆盖或NAND Flash以默认的高电平逻辑填补,给数据分析造成困扰[5]。

在某机载惯导系统6路RS232串口数据的存储系统设计中,要求4路波特率为 115 200 bps,2路波特率 230 400 bps,持续采集时长不低于4 h,且需低误码率与可选数据段读取。根据以上要求该系统采取了以FPGA(现场可编程门阵列)为控制核心,以NAND Flash为存储单元作为实施方案,并设计了以查找页为核心的读取方案,用户只需指定通道和时间区间即可将目标数据取出,给数据的高效处理及目标定位提供下位机方案。

1 系统原理设计

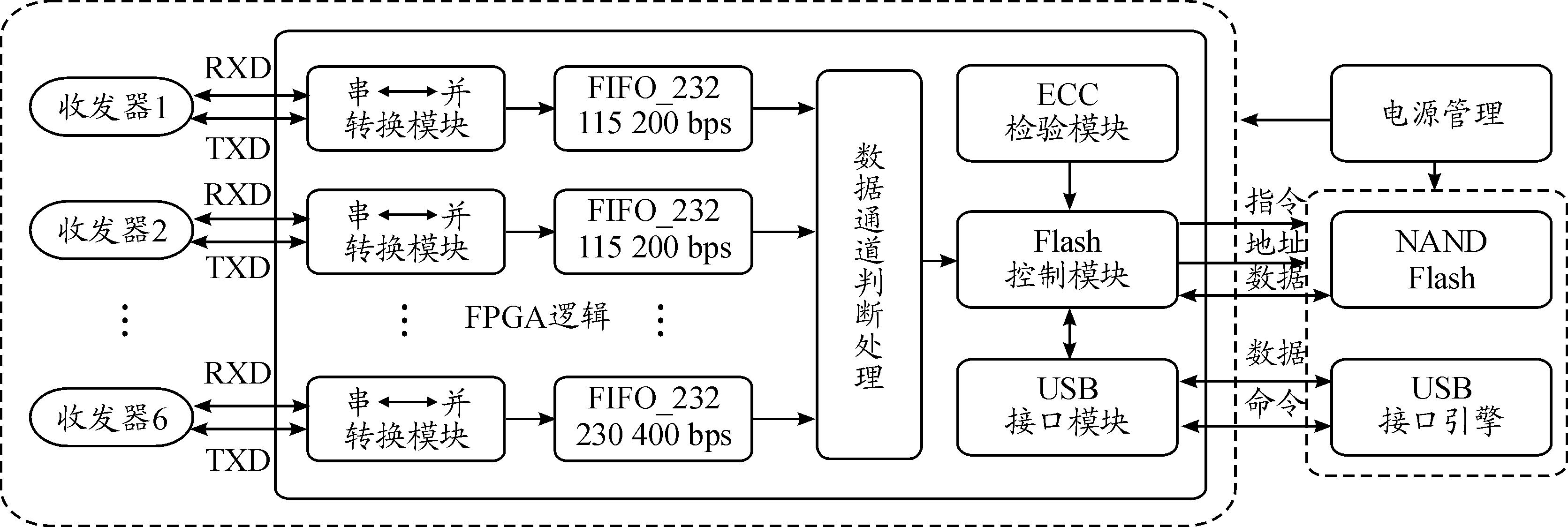

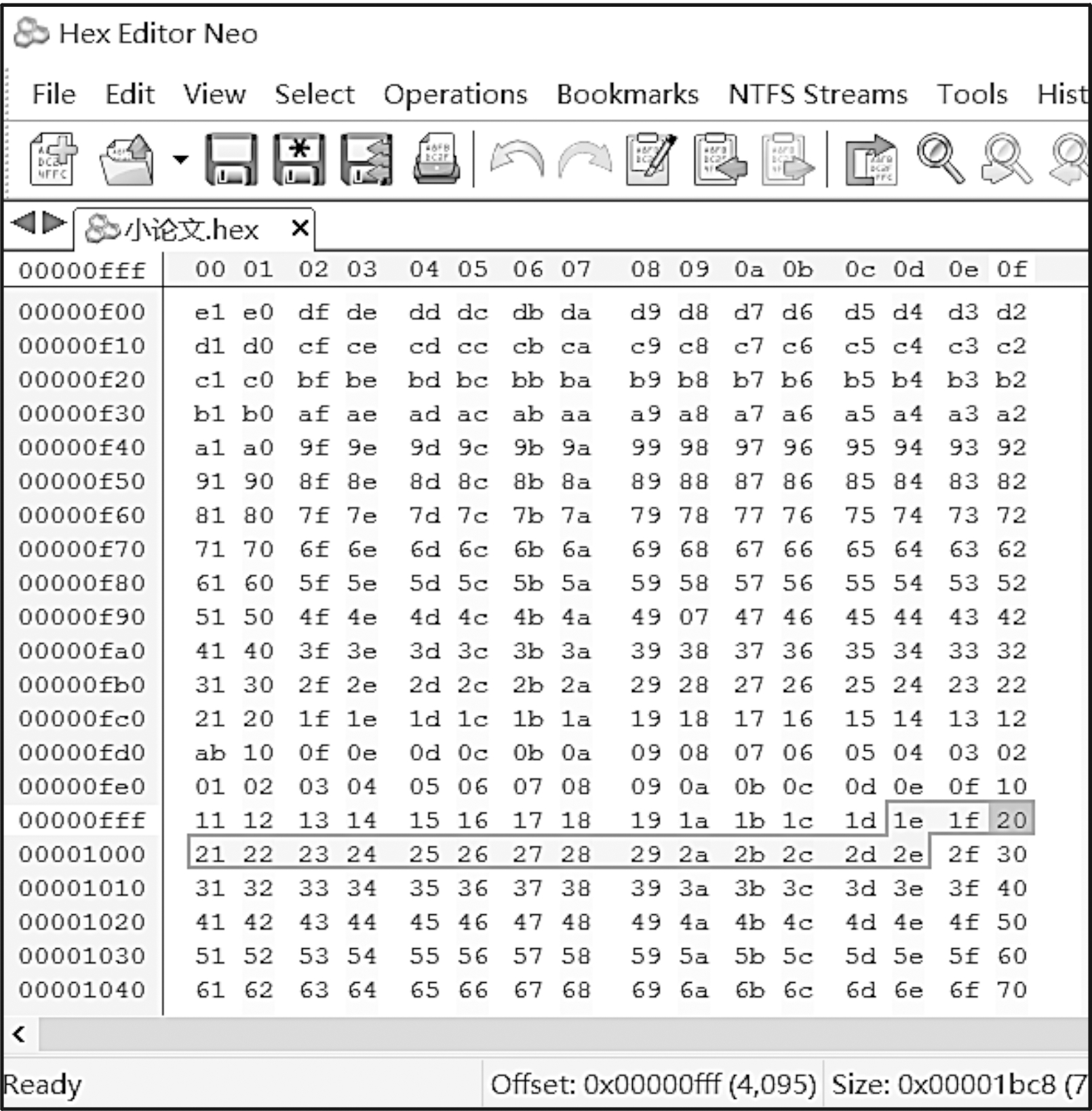

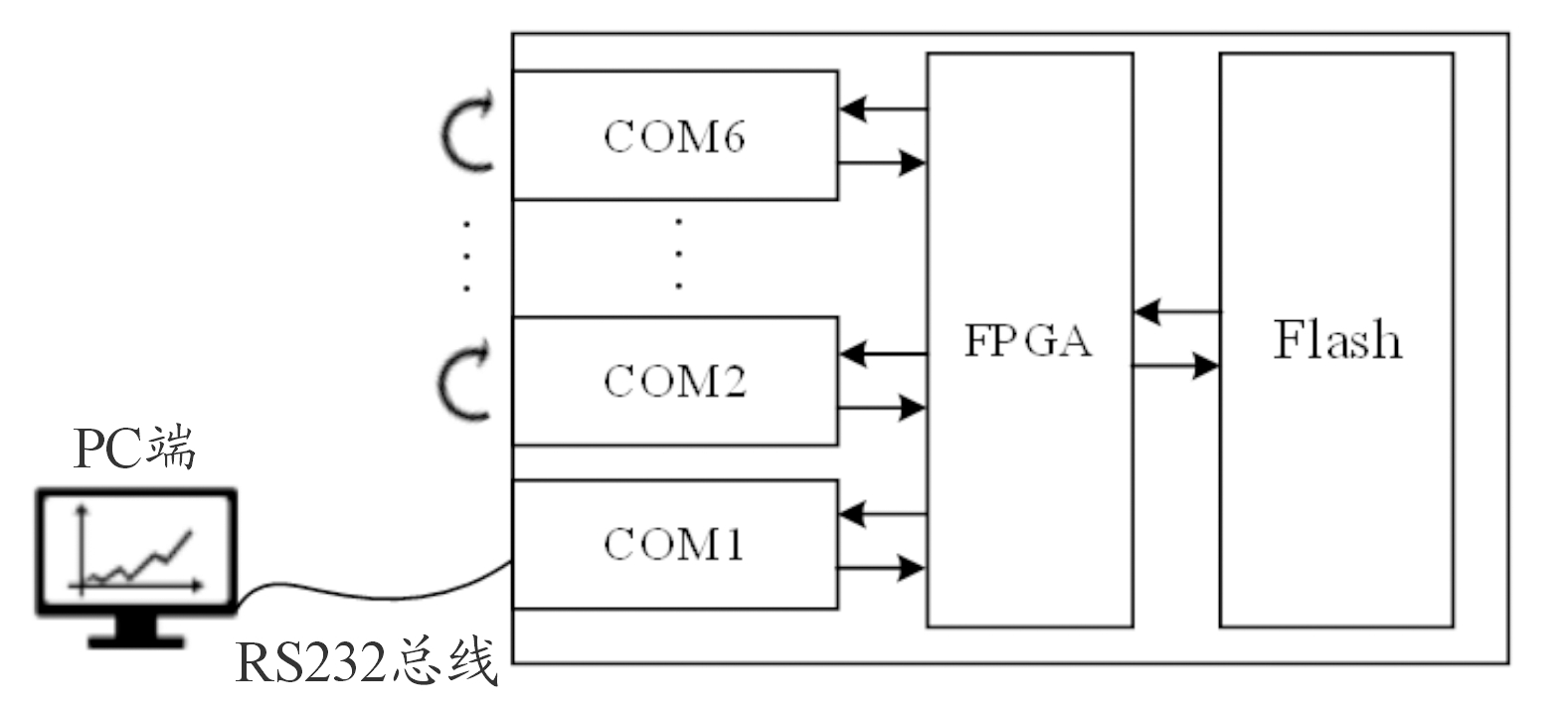

串口数据采集存储系统主要由接口模块、FPGA数据处理模块、存储模块组成,系统总体设计如图1所示。其中接口模块包括RS232串口与USB接口,RS232串口负责逻辑电平的转换与数据传输,USB接口负责上下位机的通信;FPGA模块起到数据的串并转换、通道地址分配、NAND Flash控制和人机交互的作用;存储模块以NAND Flash为介质,按采集对象的数据量选取芯片为镁光公司的MT29F16G08AB,其结构由4 096个连续块构成,每块分128页,单页可存储4 kB数据量。

其整体操作流程如下:首先系统安装并上电,采集存储系统执行初始化和自检操作;操作完成后,系统处于待记录状态,此时前端多通道串口总线接收的数据由FPGA处理并导入Flash存储单元;飞行任务结束后,上位机通过USB将数据回读至计算机。

图1 系统总体设计框图

2 系统关键技术设计

为满足机载环境下串口数据的可靠性和灵活性要求,本系统主要从软件层面展开研究,结合FPGA并行处理数据的优势,从串口数据的采集、传输、存储逻辑和数据段的选读角度进行关键技术设计。

2.1 串口数据的采集和防扰动技术

在外界环境扰动的影响下,串行总线上的数据传输可能发生误比特情况,通常这种误比特表现为总线上串入浪涌或毛刺。在串口数据的捕获处理上,虽然可在硬件上采取隔离式接口转换芯片,防范电压尖峰和接地回路的影响,但保险起见,也需要在软件设计加入防抖措施,以提高串口的抗干扰能力,降低误比特率[6]。

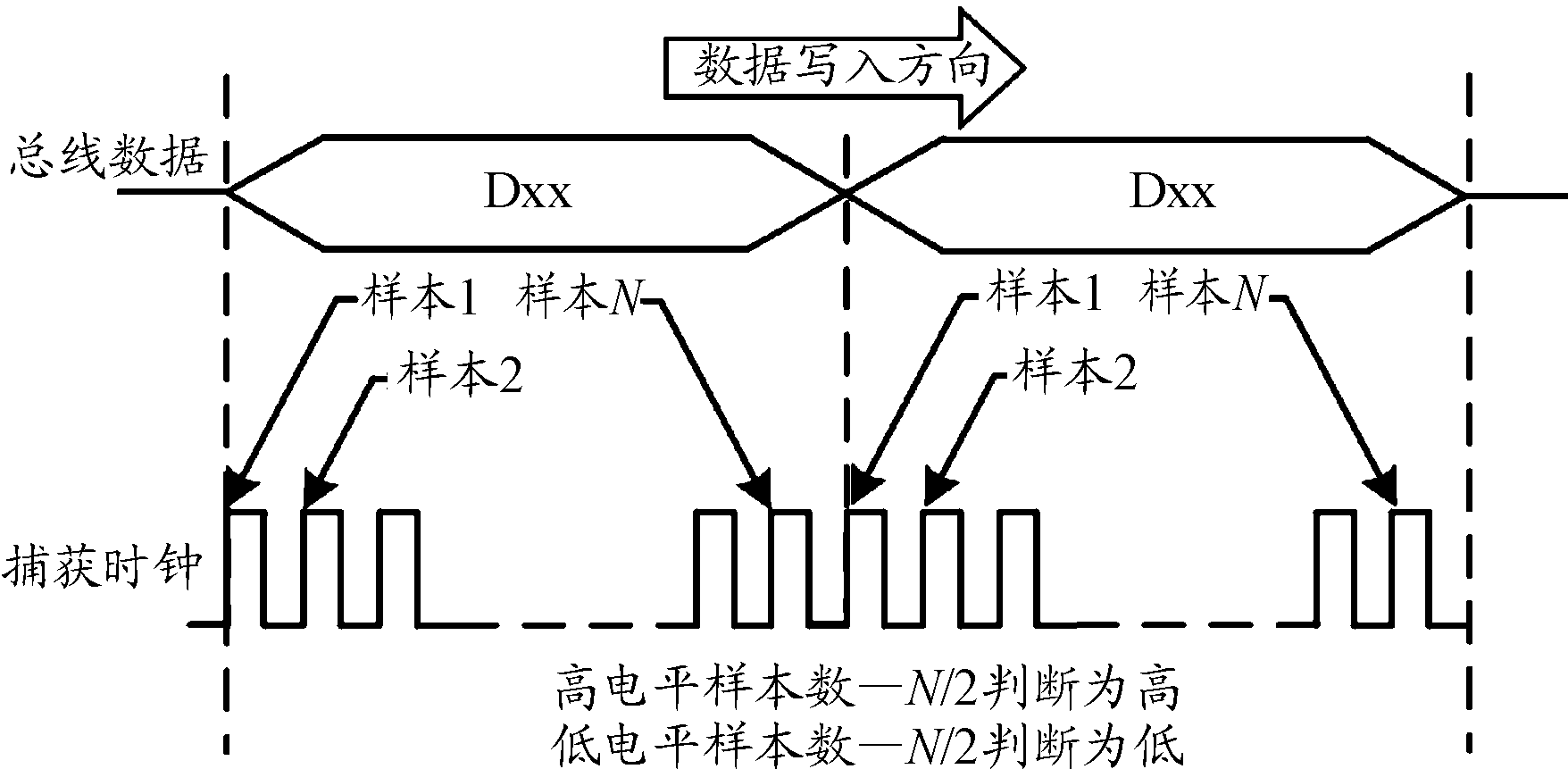

如图2所示,通常串口数据捕获采用滑窗的形式,即在固定波特率条件下,对总线上流过的每位数据进行判断采样[7]。若数据位宽为TW,则采用高出很多倍的采样时钟采集该位宽中间的极性电平,并将此电平进行串并转换解析为易于存储和传输的并行数据。本系统在捕获单位串口数据时,多次采集并统计所有采集到的电平样本的数量,通过分析样本的高低电平分布情况,判断该数据位为高逻辑电平,还是低逻辑电平。

从统计原理出发,收集的样本量越大,结论推断的可置信程度越高。同理,在采样系统中,若提高了接口的采样率,增加单位时间内接口采样的样本数,通过样本数的概率分布情况就可以很有效地揭示数据的真实性,准确判断串口极性电平[8]。

图2 串口数据捕获处理示意图

2.2 二级FIFO缓存技术

6通道波特率最高为230 400 bps,20 MHz的主控时钟下Flash的全速写入速度为4.07~10.11 MB/s,远高于6路RS232串口的数据量115 KB/s。但为避免多个串口主动同时“抢占”Flash接口而导致数据丢帧,本文引入2级缓存结构,将主动“抢占”转换为被动入栈方式。

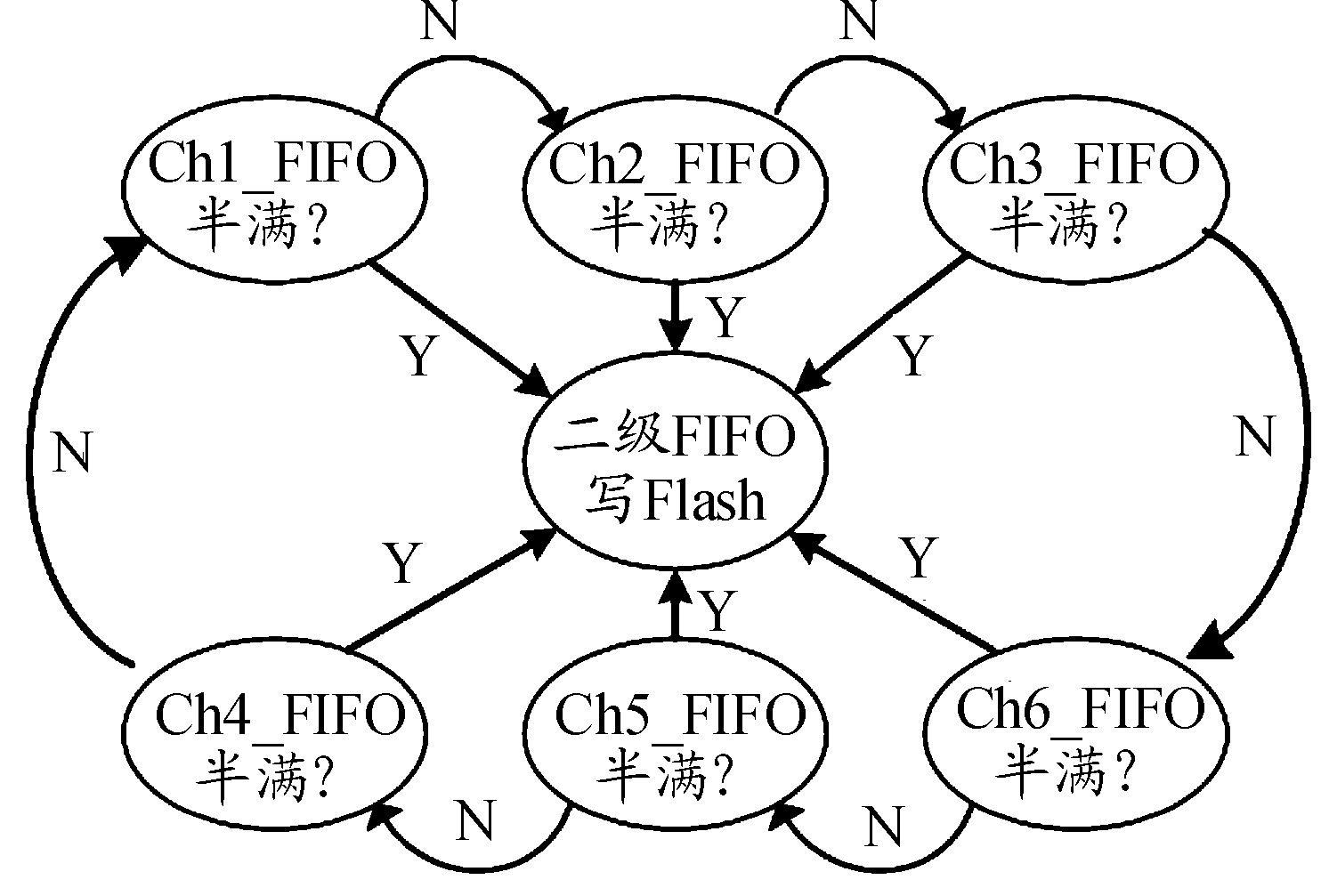

在FPGA内部有丰富的块RAM资源和IP核供使用,利用IP核生成FIFO(先入先出的双端口缓冲器)有助于提高代码的稳定性和效率[9]。二级FIFO缓存结构如图3所示,各级FIFO深度为8k,分配工作如下:各通道第1级FIFO缓存来自串并转化后的8位并行数据,当有第1级FIFO空间半满时,将该FIFO内4k数据全部取出并写入第2级FIFO缓存。在Flash处于可页编程状态时,数据立即写入Flash,2级FIFO清空。由于Flash页编程繁忙时间tPROG为200~600 μs,FIFO的半满操作可保证在写入Flash期间不会有任何一级FIFO溢出,避免了竞争,实现了Flash写操作的缓存处理。

图3 二级FIFO缓存结构示意图

2.3 Flash存储逻辑设计

针对多通道数据的读写与Flash管理机制,系统主要从以下三方面展开对NAND Flash存储逻辑设计。

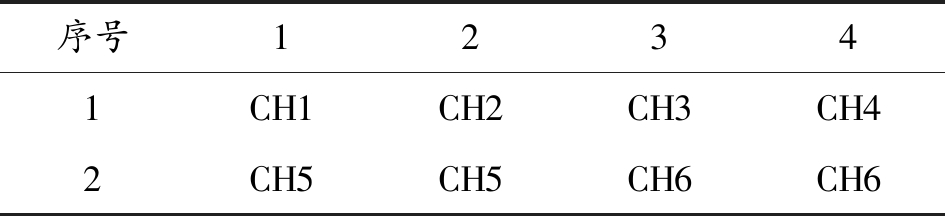

1) Flash地址指定通道方法。如表1所示,该方法将通道号与页地址建立映射,并将页地址指定给通道,即一页只存储一个通道的数据,可以形象的描述为按“页格式”进行存储。在写操作时,当二级FIFO接收到某通道的4K数据时,FPGA按此格式进行页地址指定。在读操作时,单通道数据可根据该映射关系从对应空间内取出。MT29F16G08AB内每块分128页,每8页即可完成一个循环,单块构成16次循环,按此方式便将块内地址划分为6个空间,各通道数据互不影响,相当于每个通道都有一个独立的空间[10]。

表1 页查找

序号12341CH1CH2CH3CH42CH5CH5CH6CH6

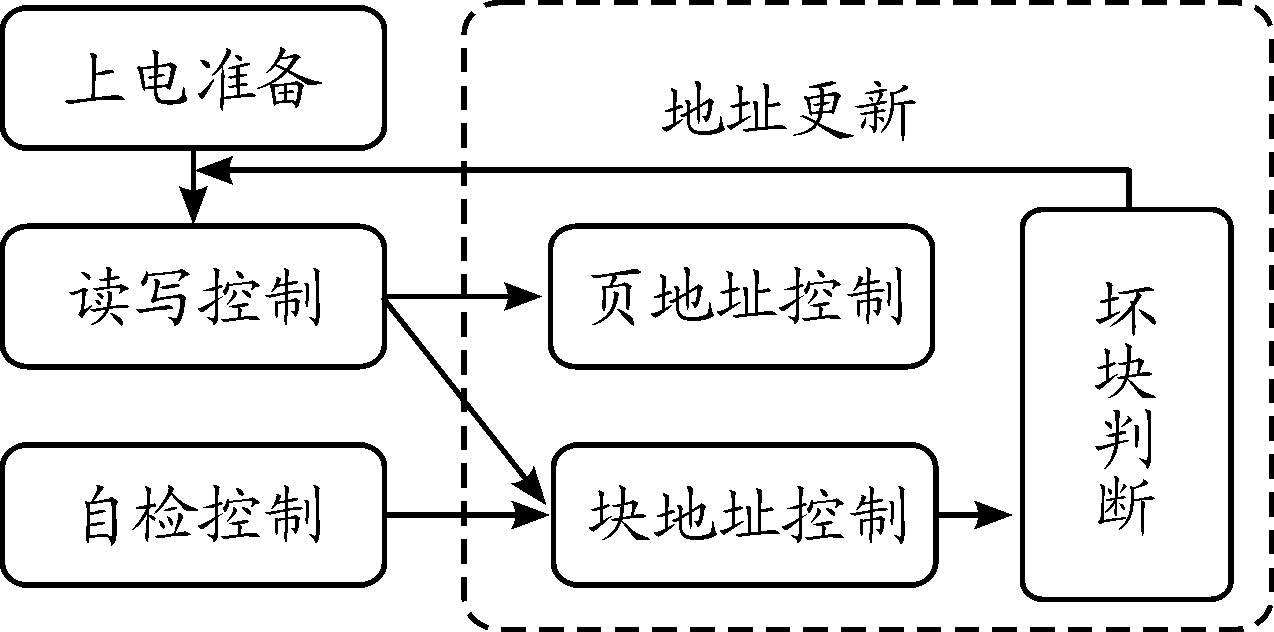

2) 数据附属信息记录。在多路数据按对应空间读写时,为保证可靠性和灵活性,分空间内的数据起始位置、空间大小以及Flash坏块信息等作为附属信息也需一并记录。由于Flash第一块在出厂时认定合格,故将该块单独设置为标记块以记录数据附属信息。当第一块因多次擦除成为无效块时,则寻找下一个好块设为标记块。系统中NAND Flash操作流程如图4所示。

图4 Flash操作流程框图

当存储系统进入上电准备状态时,需执行必要的复位和初始化操作,随后FPGA读出标记块内的附属信息,Flash进入工作状态并等待指令。在自检命令下达后,执行无效块检测、擦除操作与更新坏块信息。在读写操作时,数据需经过ECC校验处理后方可写入Flash;读写结束后,各通道附属信息开始更新。

3) 地址更新控制。由于NAND Flash读写操作以页为基础单位、擦除操作以块为单位,系统针对不同需求建立了Flash的地址更新控制器,图5为地址更新控制器结构框图,主要由页地址控制、块地址控制、和坏块判断构成。

图5 地址更新控制器结构框图

页地址控制主要用于数据与附属信息的读写,无论是记录附属信息还是读写数据,初始地址都为上电时设置的对应页。在读写阶段,若当前页操作完毕,则准备好下一个对应页继续执行; 块地址控制用于块地址更新,在自检阶段需顺序检测、擦除所有块;在Flash读写阶段,若当前块操作完毕后,则顺序开辟下一个好块以做准备。坏块判断作用于块地址需要更新的场合,读写阶段的每一块都需要与读出的坏块表进行对比,直到判断为好块方可继续执行。

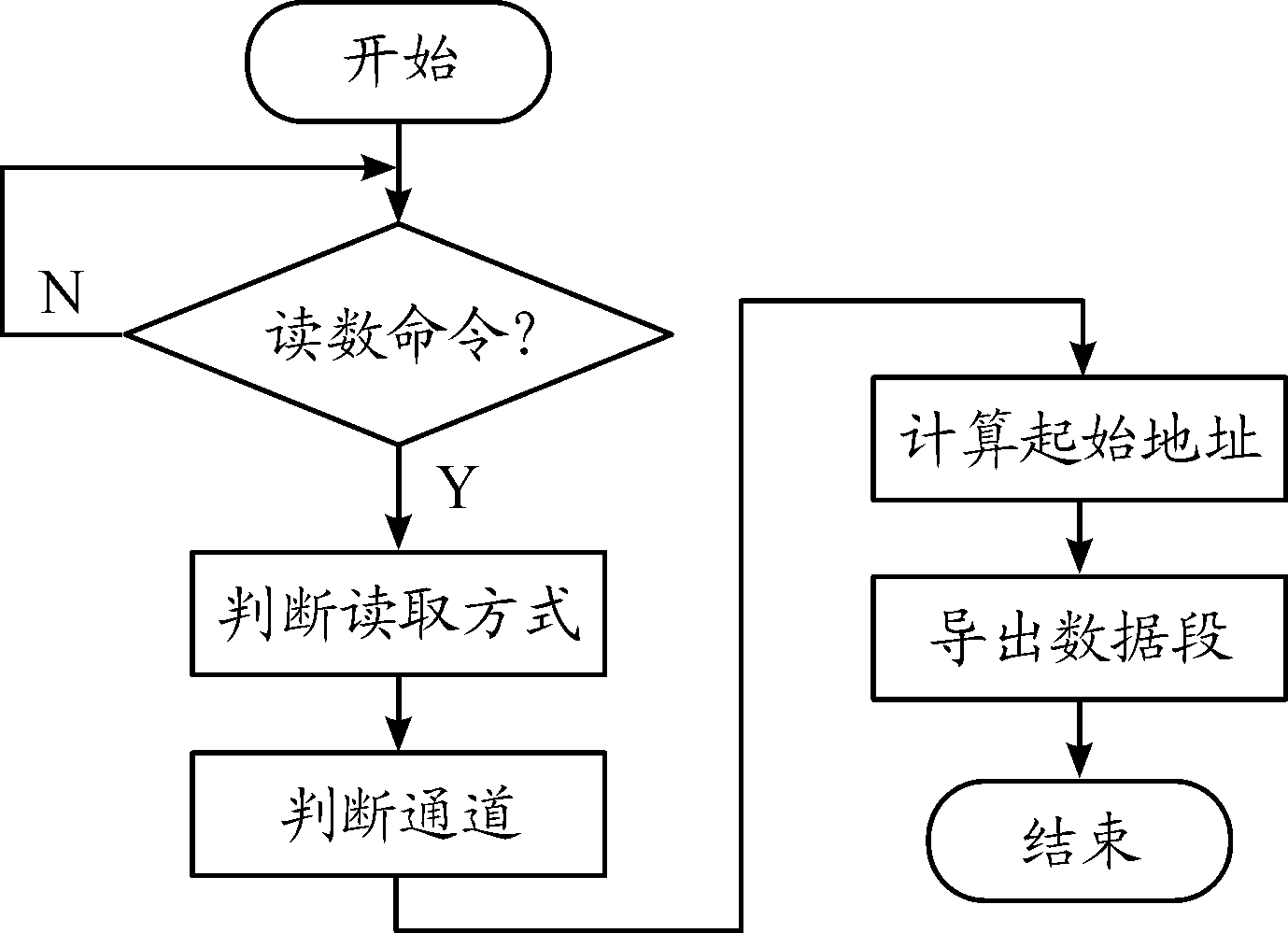

2.4 数据快速选读设计

为实现关键数据的快速定位与灵活读取,除按通道顺序读数外,系统另设计了数据包寻址法和页地址直接寻址法作为数据段的快速选读手段。数据的读取流程如图6所示,在每次数据回读时,存储系统都会判断所选读取方式和通道,再通过计算起始页地址将对应数据段导出。

图6 数据段读取流程框图

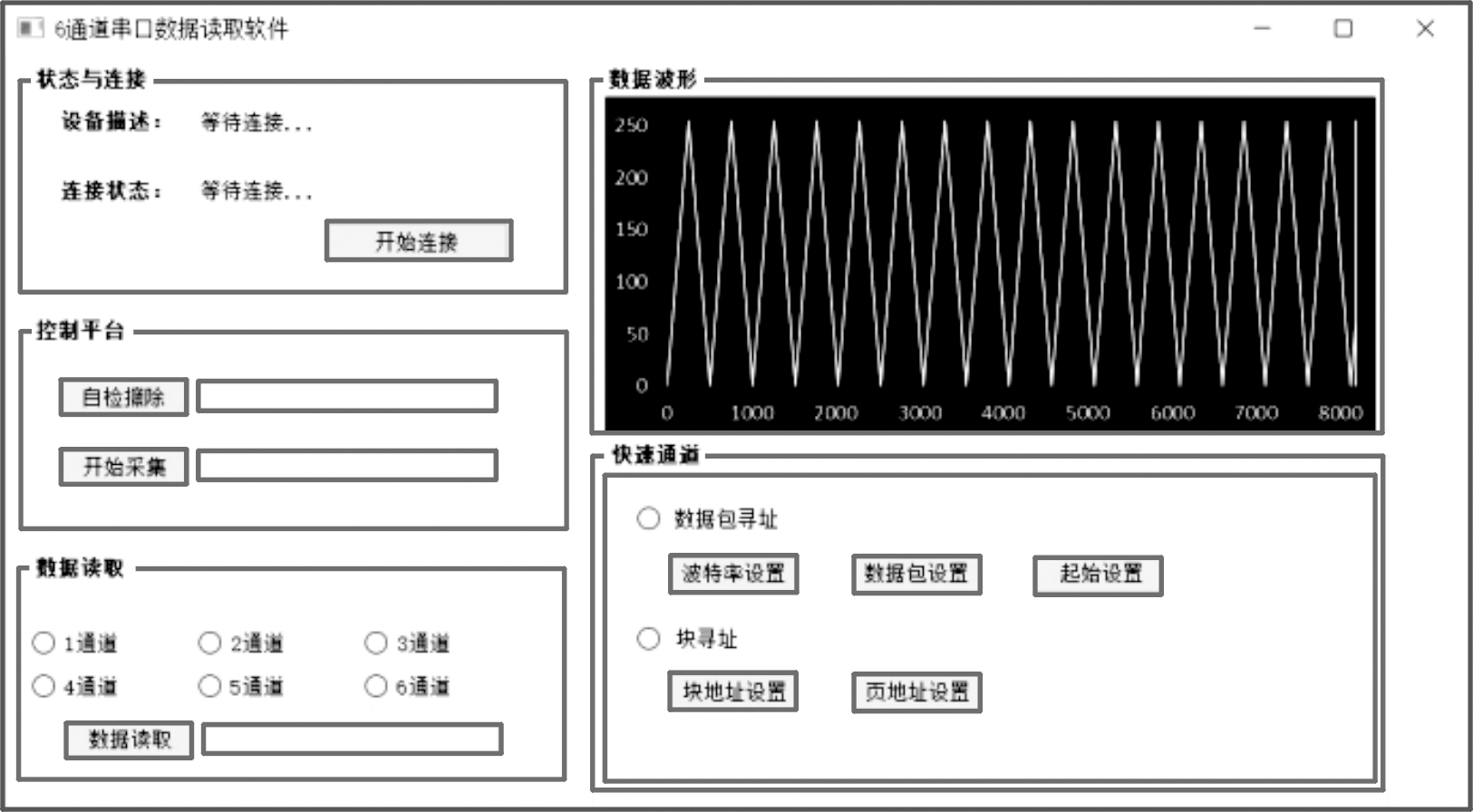

数据快速选读的核心为根据回读参数计算关键数据的起始页地址。如图7串口数据读取软件所示,在数据包寻址法中,需输入数据包的波特率、容量、频率和起始时间参数,其中波特率、包容量、频率可计算出平均写入速率,结合输入的起始时间便可得出起始地址。在页地址直接寻址法中,直接输入起始地址即可将对应地址的数据段读出。

图7 串口数据读取软件

3 实验测试和结果分析

3.1 多通道写逻辑功能测试

多通道写入功能测试是为验证各通道的数据写机制是否正常,同时也是对系统设计原理以及地址指定通道逻辑的综合考量。在多通道数据写入机制测试中,用FPGA分频得出的相应波特率发送正弦波数字信号(16位)、用系统6通道同时记录该信号并顺序从第一页开始读出,结果如图8所示: 其中CH1~CH4数据一致,CH5与CH6波形一致且数据量为前4通道的两倍,符合波特率设定。在地址指定通道的方式下,各通道各司其职,Flash地址空间分区正常,数据存储机制按表1格式正常执行。

图8 写入机制测试结果曲线

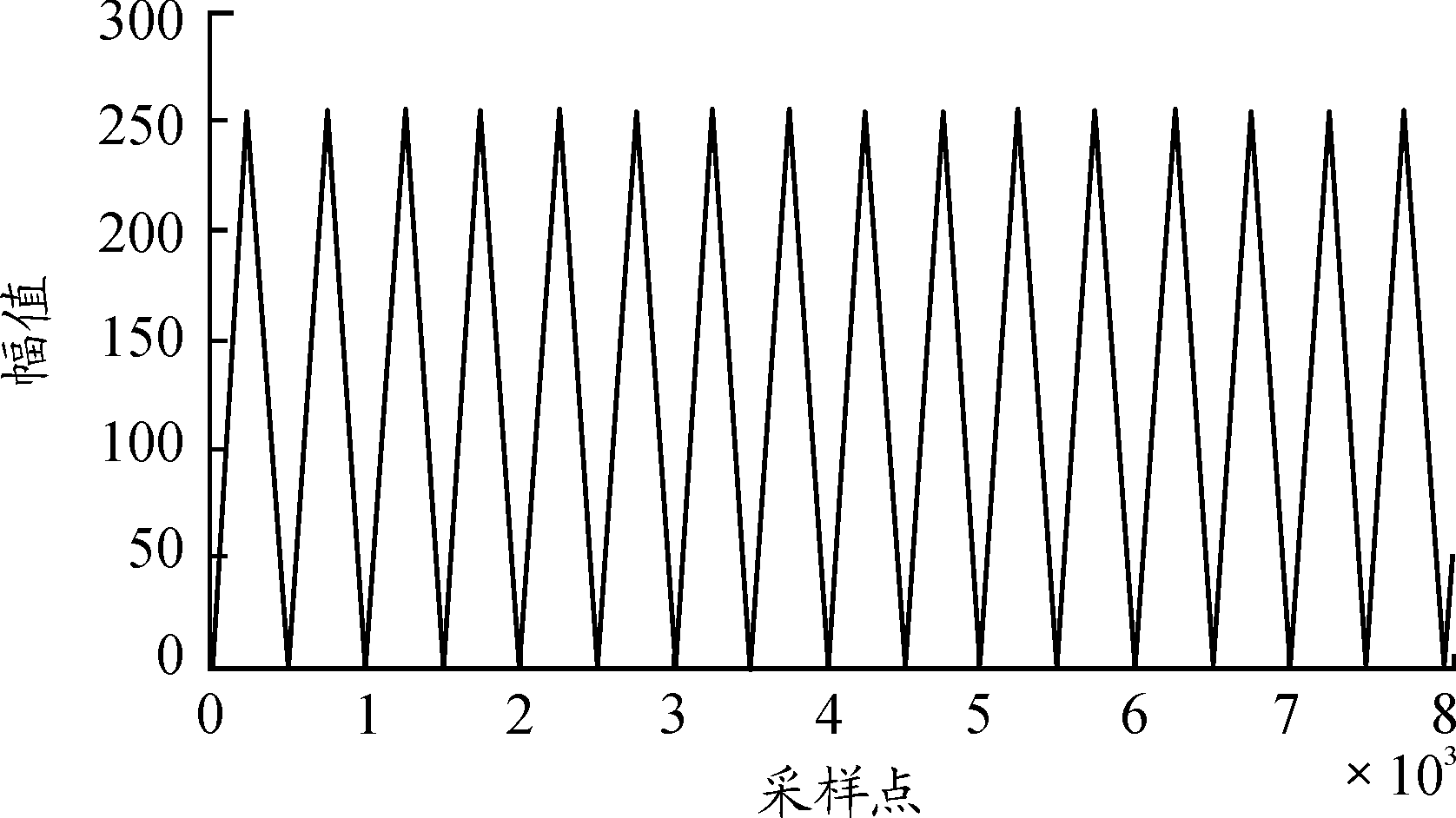

3.2 数据完整性测试

在验证各通道数据存储系统数据的完整性实验过程中,为清晰检测数据存储和传输过程的丢帧现象,用FPGA循环生成1~255递增随后递减至1的508bytes数字锯齿波传输给6各通道并写入Flash,并用USB接口将第1通道数据读出。打开上位机接收到的数据,图9为某块前两页的锯齿波形,图10为该波形在跨页衔接部分的数据,可知:在单位页的空间内,该函数共产生8个周期余32byte,地址为与理论计算结果一致;且数据的跨页衔接未发生溢出或丢失现象,数据完整可靠。

图9 局部锯齿波形

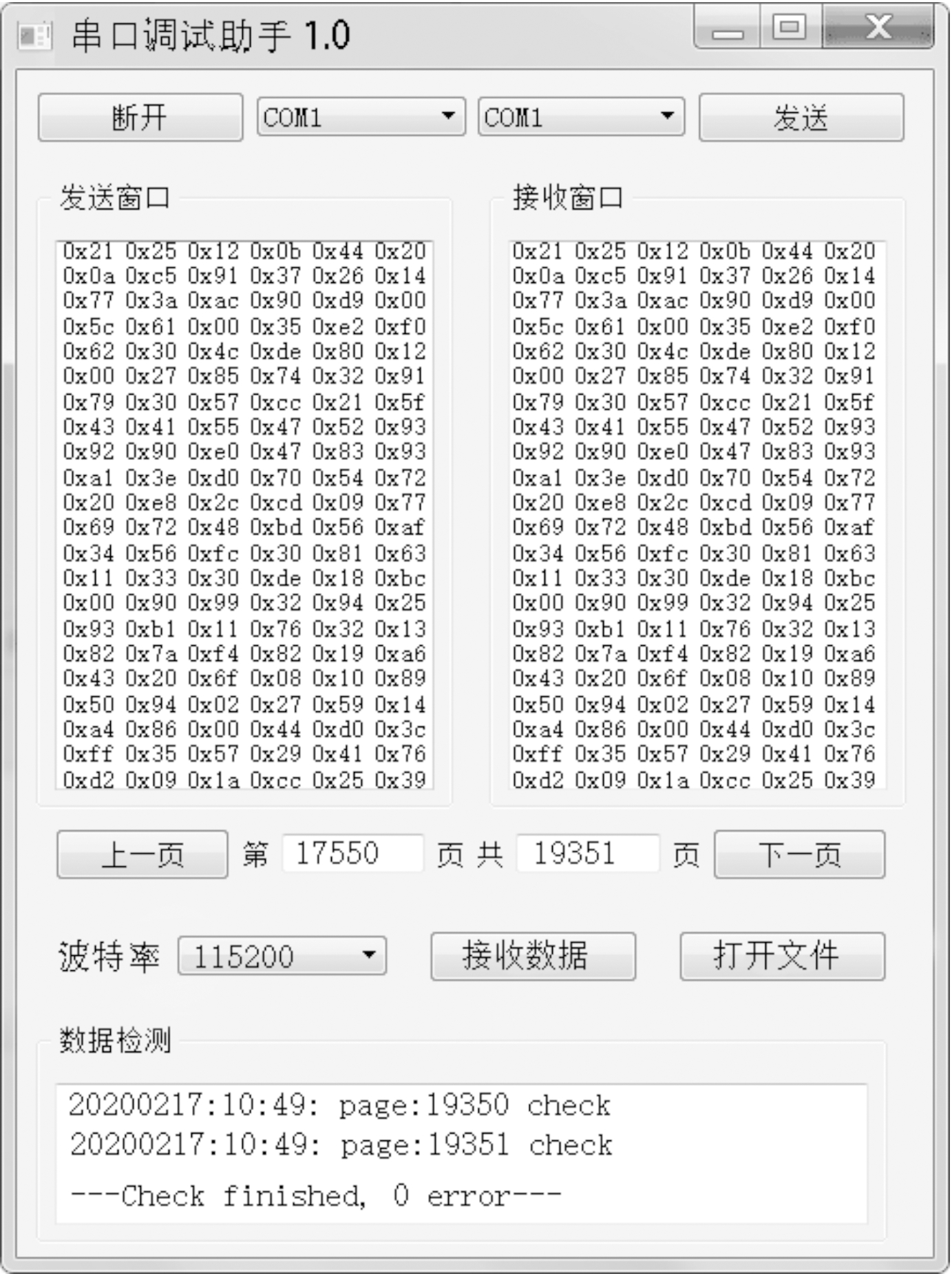

3.3 整体数据检验测试

整体数据检验测试是测试存储系统全通道长时间工作的整体误码率,同时也是对采集存储系统可靠性与稳定性的综合考量。为达到验证目的,搭建了如图11所示的测试平台:其中PC端与采集存储系统的某通道采用串口总线连接,PC端调试助手以4 096字节为一组不断向采集存储系统发送随机数据。采集系统其他通道按该随机数据自发送与自接收。数据发送停止后,调试助手同样以4 096字节为一组读取任一通道存储单元内数据,并与预置随机数据对比。

图10 锯齿波数据完整性分析界面

图11 测试实验平台示意图

为对照测试结果,调试助手保留了源随机数据记录,并与读出数据进行对比分析,图12为某页测试结果。可知:采集系统经长时间工作后,源数据与接收数据仍保持一致,该通道无出现误比特的现象,满足了预期要求,达到多路串口同时采集及存储的目的,并验证了存储模型的正确性。

图12 整体数据检验测试界面

4 结论

本系统以多通道串口系统的新存储要求展开研究,以FPGA为主控核心设计了6通道RS232串口数据的采集、缓存及存储系统。同传统写入方法相比,系统通过地址指定通道的思想将单片Flash空间分区,实现了各通道地址上的相互独立。最后通过数据写入机制测试、完整性测试和整体数据检验测试验证了存储模型的可行性,测试结果表明该系统采集和存储数据的准确率高,处理多通道大容量数据灵活、简便。

[1] 吴斌,李林,张晓艳,等.基于RS232串口的机载计算机自动测试方法[J].信息通信,2016(05):140-141.

[2] 邓竑杰.多路串口到以太网的数据网关的设计与实现[D].昆明:云南大学,2014.

[3] 周之丽.基于NAND Flash的大容量存储装置的设计与研究[D].太原:中北大学,2015.

[4] 王晓楠.弹载多通道数据采集系统的研究[D].中北大学,2018.

[5] 李远哲,贺海文,万丽,等.嵌入式系统大容量NAND Flash存储器分区管理设计[J].计算机测量与控制,2019,27(02):212-215,220.

[6] 武文斌,陈先玉.4~20 mA电流环串行通信接口抗干扰研究[J].现代电子技术,2014,37(12):116-118.

[7] 尤雪芬.数据采集与波形处理软件设计[D].成都:电子科技大学,2013.

[8] 郭敏,庄信武,王向东,等.基于FPGA的多通道串口数据采集与传输设计[J].计算机测量与控制,2017,25(11):186-189.

[9] 吕迎春,谭庆贵,谢军,等.光纤通道数据采集存储系统设计与实现[J].航空电子技术,2014,45(03):17-21.

[10] 任勇峰,周涛,李辉景,等.基于Flash的侵彻关键信号分区存储方法[J].探测与控制学报,2015,37(05):106-109.

[11] 邬晓琳,余艳.多模式无线数据采集主机的开发与应用研究[J].电工技术,2019(24):38-39.